### **GE Industrial Systems**

# VSVO Servo Board

These instructions do not purport to cover all details or variations in equipment, nor to provide for every possible contingency to be met during installation, operation, and maintenance. The information is supplied for informational purposes only, and GE makes no warranty as to the accuracy of the information included herein. Changes, modifications, and/or improvements to equipment and specifications are made periodically and these changes may or may not be reflected herein. It is understood that GE may make changes, modifications, or improvements to the equipment referenced herein or to the document itself at any time. This document is intended for trained personnel familiar with the GE products referenced herein.

GE may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not provide any license whatsoever to any of these patents. All license inquiries should be directed to the address below. If further information is desired, or if particular problems arise that are not covered sufficiently for the purchaser's purpose, the matter should be referred to:

GE Industrial Systems Post Sales Service 1501 Roanoke Blvd. Salem, VA 24153-6492 USA Phone: + 1 888 GE4 SERV (888 434 7378, United States) + 1 540 378 3280 (International) Fax: + 1 540 387 8606 (All)

("+" indicates the international access code required when calling from outside the USA)

This document contains proprietary information of General Electric Company, USA and is furnished to its customer solely to assist that customer in the installation, testing, operation, and/or maintenance of the equipment described. This document shall not be reproduced in whole or in part nor shall its contents be disclosed to any third party without the written approval of GE Industrial Systems.

GE PROVIDES THE FOLLOWING DOCUMENT AND THE INFORMATION INCLUDED THEREIN AS IS AND WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED STATUTORY WARRANTY OF MERCHANTABILITY OR FITNESS FOR PARTICULAR PURPOSE.

Issue date: 2002-06-30

© 2002 by General Electric Company, USA. All rights reserved.

| Section                                            | Page |

|----------------------------------------------------|------|

| Functional Description                             | 2    |

| Installation                                       |      |

| Operation                                          | 5    |

| Specifications                                     |      |

| Diagnostics                                        |      |

| Configuration                                      |      |

| DSVO-Simplex DIN-rail Mounted Servo Terminal Board |      |

| Installation                                       |      |

| I/O Board Alarms                                   |      |

# **Functional Description**

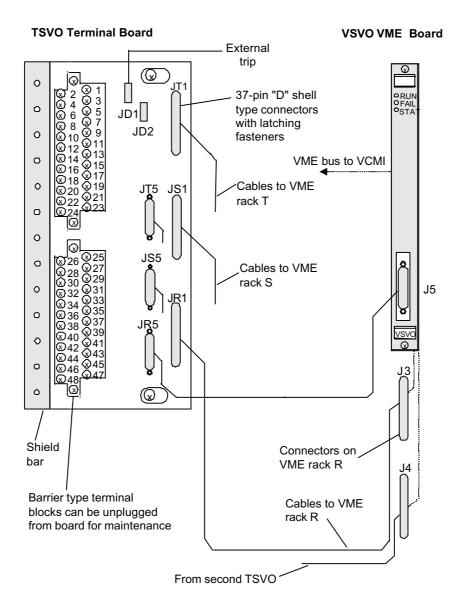

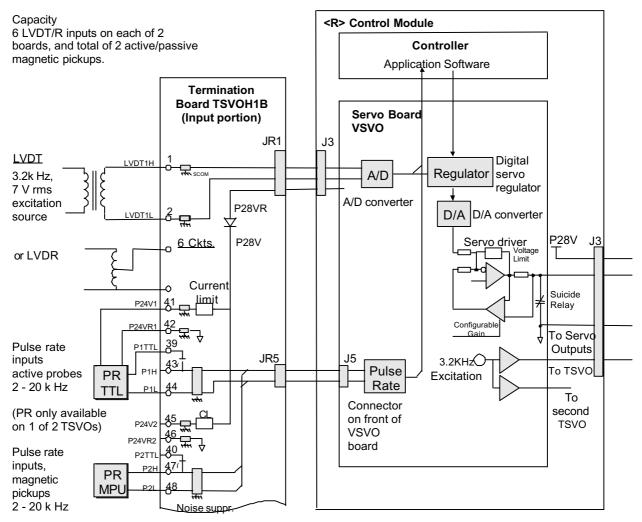

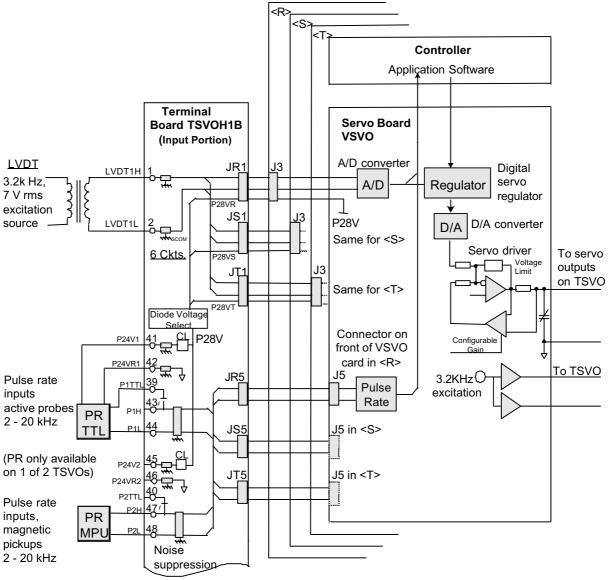

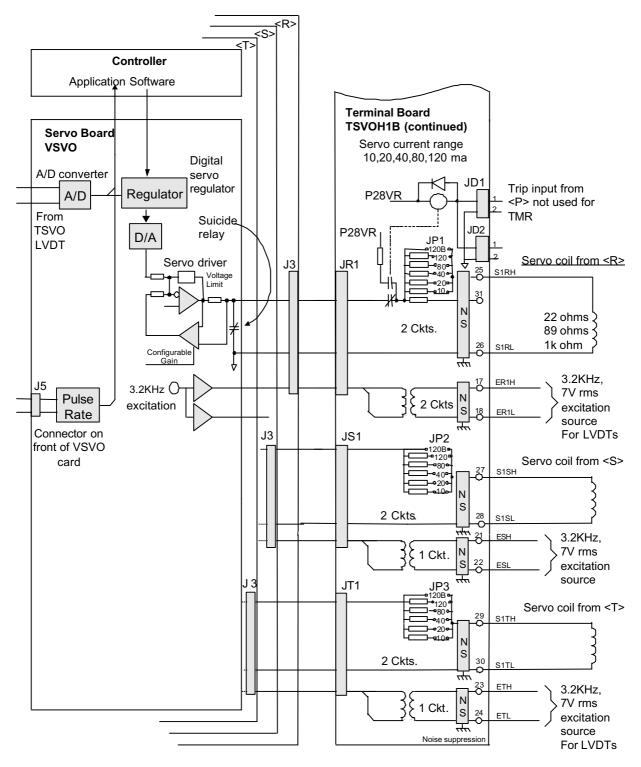

The Servo Board (VSVO) controls four electrohydraulic servo valves that actuate the steam/fuel valves. These four channels are divided between two TSVO terminal boards. Valve position is measured with linear variable differential transformers (LVDT). Three cables to VSVO use the J5 plug on the front on the board and the J3/4 connectors on the VME rack. TSVO provides Simplex signals via the JR1 connector, and fans out TMR signals to the JR, LS, and JT connectors. Plugs JD1 or JD2 are for external trip from the protection module.

Servo/LVDT Terminal Board, Processor Board, and Cabling

#### Installation

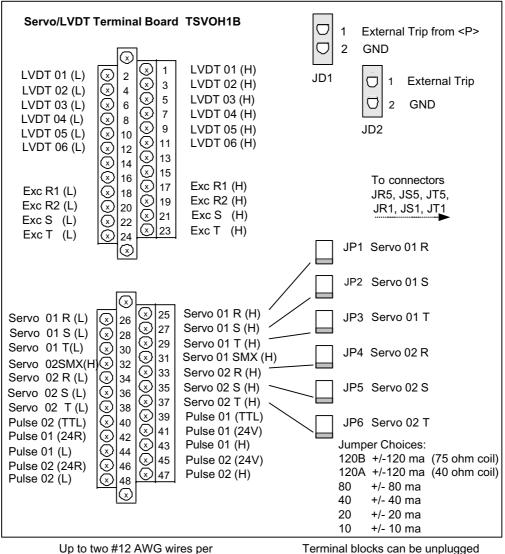

Sensors and servo valves are wired directly to two I/O terminal blocks mounted on the terminal board. Each block is held down with two screws and has 24 terminals accepting up to #12 AWG shield termination strip attached to chassis ground is located immediately to the left of each terminal block. External trip wiring is plugged into either JD1 or JD2. The screw connection and position choices for the servo current jumpers.

point with 300 V insulation

Terminal blocks can be unplugged from terminal board for maintenance

Servol LVDT Terminal Board Wiring

### Operation

*Refer to the figures for inputs and outputs.*

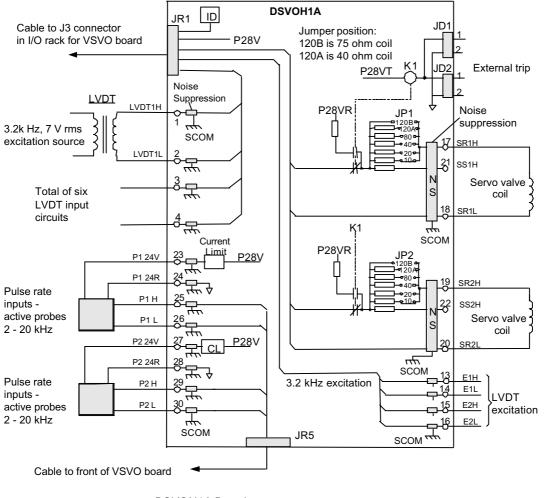

The servo board provides four channels consisting of bi-directional servo current outputs, LVDT position feedback, LVDT excitation and pulse rate flows inputs. The TSVO provides excitation for, and accepts inputs from , up to six LVDT valve position inputs. There is a choice of one, two three, or four LDTs for each servo control loop. If three inputs are used they are available for gas turbine flow measuring applications, and these signals come through TSVO and go directly to the VSVO board front at J5.

Each servo output is equipped with an individual suicide relay under firmware control that shorts the VSVO output signal to signal common when de-energized, and recovers to nominal limits after a manual reset command is issued. Diagnostics monitor the output status of each servo voltage, current and suicide relay.

LVDT and Pulse Rate Inputs, Simplex

Each of the servo output channels can drive either one or two-coil servos in Simplex applications, or two or three-coil servos in TMR applications. The two-coil TMR applications are for 200# oil gear systems where each of two control modules drive one coil each. And the third module has to servo interface. Servo cable lengths up to 300 meters (984 feet) are supported with a maximum two-way cable resistance of 15 ohms. Sine there are many types of servo coils, a variety of bi-directional current sources are jumper selectable.

Another trip override relay K1 is provided on each terminal board which is driven from the <P> Protection Module. If an emergency overspeed condition is detected in the Protection Module, the K1 relay will energize and disconnect the VSVO servo output from the terminal block and apply a bias to drive the control valve closed. This is only used on Simplex applications to protect against the servo amplifier failing high, and is functional only with respect to the servo coils driven from <R>.

<R> **Terminal Board** Controller **TSVOH1B** (continued) **Application Software** Servo Board Coil current range vsvo 10,20,40,80,120 ma A/D converter Digital JD1 P28VR A/D Regulator Trip input from servo <P> module (J1) regulator 2 4 From LVDT JD2 D/A D/A converter P28VR IP1 TSVO 20B Servo coil from<R> Servo driver JR1 .13 25 Voltage S1RH Limit 31 22 ohms 1 k 2 Ckts 89 ohms P28V ohm 1k ohm 26 S1RI Configurable С 17 ER1H 3.2KHz, J5 3.2KHz C Pulse Ν 7V rms ξ Excitation s 18 excitation Rate ER1L source 2 Ckts for LVDTs Connector on Noise front of VSVO suppr-То ession second TSVO

Servo Coil and LVDT Outputs, Simplex (continued) LVDT Outputs, Simplex (continued)

Only two pulse rate probes on one TSVO are used.

The primary and emergency

overspeed systems will trip

independent of this circuit.

the hydraulic solenoids

In TMR Applications, the LVDT signals on TSVO fan out to three racks through JR1, JS1, and JT1. Thee connectors also bring power into TSVO where the three voltages are diode high-selected and current limited to supply 24 V dc to the pulse rate active probes.

LVDT and Pulse Rate Inputs, TMR

For TMR systems, each servo channel has connections to three output coils with a range of current ratings up to 120 mA selected by jumper.

Servo Coil Outputs and LVDT Excitation, TMR

Servo Coil Ratings

| Coil<br>Type | Nominal<br>Current  | Coil Resistance<br>(Ohms) | Internal Resistance<br>(Ohms) | Application     |

|--------------|---------------------|---------------------------|-------------------------------|-----------------|

| 1            | $\pm$ 10 mA         | 1,000                     | 180                           | Simplex and TMR |

| 2            | $\pm 20 \text{ mA}$ | 125                       | 442                           | Simplex         |

| 3            | $\pm 40 \text{ mA}$ | 62                        | 195                           | Simplex         |

| 4            | $\pm 40 \text{ mA}$ | 89                        | 195                           | TMR             |

| 5            | $\pm$ 80 mA         | 22                        | 115                           | TMR             |

| 6            | $\pm$ 120 mA (A)    | 40                        | 46                            | Simplex         |

| 7            | $\pm$ 120 mA (B)    | 75                        | 10                            | TMR             |

The total resistance would be equivalent to the standard setting.

The excitation source is isolated from signal common (floating) and is capable of operation at common mode voltages up to 35 V dc, or 35 V rms, 50/60 Hz.

The software limit check is adjustable in the field.

The maximum short circuit current is approximately 100 mA with a maximum power output of 1 watt. The following table defines the standard servo coil resistance and their associated internal resistance, selectable with the terminal board jumpers shown in the figure above. In addition to these standard servo coils, it is possible to drive non-standard coils by using a non-standard jumper setting. For example, an 80 mA, 125-ohm coil could be driven by using a jumper setting 120B.

Control valve position is sensed with either a four wire LVDT or a three-wire linear variable differential reluctance (LVDR). Redundancy implementations for the feedback devices is determined by the application software to allow the maximum flexibility. LVDT/Rs can be mounted up to 300 meters (984 feet) from the turbine control with a maximum two-way cable resistance of 15 ohms.

Two LVDT/R excitation sources are located on each terminal board for Simplex applications and another two for TMR applications. Excitation voltage is 7 V rms and the frequency is 3.2 kHz with a total harmonic distortion of less than 1% when loaded.

A typical LVDT/R has an output of 0.7 V rms as the zero stroke position of the valve stem, and an output of 3.5 V rms at the designed maximum stoke position (some applications have these reversed). The LVDT/R input is converted to dc and conditioned with a low pass filter. Diagnostics perform a high/low (hardware) limit check on the input signal and a high/low system (software) limit check.

Two pulse rate inputs are cabled to a single J5 connector on the VSVO board front. This is a dedicated connection to minimize noise sensitivity on the pulse rate inputs.

Inputs support both passive magnetic pickups and active pulse rate transducers (TTL type) interchangeably without configuration. Normally, these inputs are not used on steam turbine applications, but are usually for liquid fuel flow measurement, and monitoring flow divider feedback in gas turbine applications. Pulse rate inputs can be located up to 300 meters (984) from the turbine control cabinet; this assumes shielded-pair cable is used with typically 70 nF single ended or 35 nF differential capacitance and 15 ohms resistance.

A frequency range of 2 to 30 kHz can be monitored at a normal sampling rate of either 10 or 20 ms. Magnetic pickups typically have an output resistance of 200 ohms and an inductance of 85 mH excluding cable characteristics. The transducer is a high impedance source, generating energy levels insufficient to cause a spark.

## Specifications

| S                            | Specifications                                                                                                                                                        |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ltem                         | Specification                                                                                                                                                         |

| Number of inputs (per TSVO)  | 6 LVDT windings<br>2 pulse rate signals (total of 2 per VSVO)<br>External trip signal                                                                                 |

| Number of outputs (per TSVO) | 2 servo valves (total of 4 per VSVO board)<br>4 excitation sources for LVDTs<br>2 excitation sources for pulse rate transducers                                       |

| Internal sample rate         | 200 Hz                                                                                                                                                                |

| Power supply voltage         | Nominal 24 V dc                                                                                                                                                       |

| LVDT accuracy                | 1 % with 14-bit resolution                                                                                                                                            |

| LVDT input filter            | Low pass filter with 3 down breaks at 50 rad/sec $\pm 15\%$                                                                                                           |

| LVDT common mode rejection   | CMR is 1 V, 60 dB at 50/60 Hz                                                                                                                                         |

| LVDT excitation output       | Frequency of 3.2 +/- 0.2 kHz<br>Voltage of 7.00 +/- 0.14 V rms                                                                                                        |

| Pulse rate accuracy          | 0.05% of reading with 16-bit resolution at 50 Hz frame rate Noise of acceleration measurement is less than $\pm$ 50 Hz/sec for a 10,000 Hz signal being read at 10 ms |

| Pulse rate input             | Minimum signal for proper measurement at 2 Hz is 33 mVpk, and at 12 kHz is 827 mVpk.                                                                                  |

| Magnetic PR pickup signal    | Generates 150 V p-p into 60 K ohms                                                                                                                                    |

| Active PR Pickup Signal      | Generates 5 to 27 V p-p into 60 K ohms                                                                                                                                |

| Servo valve output accuracy  | 2% with 12-bit resolution Dither amplitude and frequency adjustable                                                                                                   |

| Fault detection              | Suicide servo outputs initiated by:<br>Servo current out of limits or not responding<br>Regulator feedback signal out of limits                                       |

### Diagnostics

Three LEDs at the top of the VSVO front panel status information. The normal RUN condition is a flashing green, and FAIL is solid red. The third LED is normally off but displays a steady orange if an alarm condition exists on the board

Servo diagnostics cover items such as out of range LVDT voltage, servo suicide, servo current open circuit, and short circuit. If any one of the signals goes unhealthy a composite diagnostic alarm, L#DIAG\_VSVO occurs. If the associated regulator has two sensors, the bad sensor is removed from the feedback calculation and the good sensor is used. Details of the individual diagnostics are available from the toolbox. The diagnostic signals can be individually latched, and reset with the RESET\_DIA signal if they go healthy

Connectors Jr1, JS1, JT1 on the terminal board have their own ID device that is interrogated by the I/O board. The ID device is a read-only chip coded with the terminal board serial number, board type, revision number, and the plug location.

# Configuration

The VSVO module is configured using the toolbox. This software usually runs on a data-highway connected CIMPLICITY station or workstation. The following table defines the configuration choices and defaults. For details refer to GEH-6403, *Control System Toolbox for Configuring the Mark VI Turbine Controller*.

Typical VSVO Configuration

| Parameter       | Description                                         | Choices                                                                                                                        |

|-----------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Configuration   |                                                     |                                                                                                                                |

| System Limits   | Select system limits                                | Enable, disable                                                                                                                |

| Regulator 1     | LVDT/R calibration                                  | Online LVDT calibration, yes/no                                                                                                |

| RegType         | Algorithm used in the regulator                     | Unused 1_PulseRate<br>2_PlsRateMAX 1_LVPosition<br>2_LV_PosMIN 2_LV_PosMID<br>2_LvpilotCyl 4_LVp/cyIMAX<br>4_LV_LM 2_LV_posMAX |

| RegGain         | Position loop gain in (%current/%position)          | -100 to 100                                                                                                                    |

| RegNullBias     | Null bias in % current, balances servo spring force | -100 to 100                                                                                                                    |

| DitherAmpl      | Dither in % current (minimizes hysteresis)          | Dither amp: 0 to 10                                                                                                            |

| Monitor 1       |                                                     |                                                                                                                                |

| Monitor type    | Monitor algorithm                                   | Unused<br>1_Lvposition<br>2_LVposMIN<br>2_LVposMAX<br>3_LVposMID<br>1_LvposRatio<br>2_LVposRatio                               |

| J3:IS200TSVOH1A | Terminal board 1 connected to VSVO through J3       | Connected, not connected                                                                                                       |

| Servo Output1   | Measured output current in percent – Board point    | Point edit (input FLOAT)                                                                                                       |

| Reg Number      | Identify regulator number                           | Unused, Reg1, Reg2, Reg3, Reg4                                                                                                 |

| Servo_MA_Out    | Select current output for coil windings             | 10, 20, 40, 80, 120 mA                                                                                                         |

| EnableCurSuic   | Select Suicide function based on current            | Enable, disable                                                                                                                |

| Curr_Suicide    | Percent current error to initiate suicide           | 0 to 100% (output current error)                                                                                               |

| EnablFbkSuic    | Select Suicide function based on feedback           | Enable, disable                                                                                                                |

| Fdbk_Suicide    | Percent position error to initiate suicide          | 0 to 100% (actuator position error)                                                                                            |

| Servo Output2   | Measured output current in percent - Board point    | Point edit (input FLOAT)                                                                                                       |

| J4:IS200TSVOH1A | Terminal Board 2 connected to VSVO via J4           | Connected, not connected                                                                                                       |

| Servo Output3   | Servo current output wired to valve - Board point   | Point edit (input FLOAT)                                                                                                       |

| Servo Output4   | Servo current output wired to valve - Board point   | Point edit (input FLOAT)                                                                                                       |

| J5:IS00TSVOH1A  | Pulse Rate inputs cabled to J5 connector            | Connected, not connected                                                                                                       |

|         | FlowRate1      | Pulse rate input selected - Board point            | Point edit (input FLOAT) |       |

|---------|----------------|----------------------------------------------------|--------------------------|-------|

|         | PRType         | Select speed or flow type signal                   | Unused, speed, or flow   |       |

|         | PRScale        | Convert Hz to engineering units                    | 0 to 1,000               |       |

|         | SysLim1Enabl   | Select system limit                                | Enable, disable          |       |

|         | SysLim1Latch   | Select whether alarm will latch                    | Latch, not latch         |       |

|         | SysLim1Type    | Select type of alarm initiation                    | >= or <=                 |       |

|         | SysLimit       | Select alarm level in GPM or RPM                   | 0 to 12,000              |       |

|         | SystemLim2     | Same as above                                      | Same as above            |       |

|         | TMR_DiffLimt   | Difference limit off voted pulse inputs (EU)       | 0 to 12,000              |       |

|         | FlowRate2      | Pulse rate input selected - Board point (as above) | Point edit (input FLOAT) |       |

| Board I | Points Signals | Description - Point Edit (Enter Signal Connection) | Direction                | Туре  |

|         | L3DIAG_VSVO1   | Board diagnostic                                   | Input                    | BIT   |

|         | L3DIAG_VSVO2   | Board diagnostic                                   | Input                    | BIT   |

|         | L3DIAG_VSVO3   | Board diagnostic                                   | Input                    | BIT   |

|         | SysLim1PR1     | Process alarm                                      | Input                    | BIT   |

|         | SysLim2PR1     | Process alarm                                      | Input                    | BIT   |

|         | SysLim1PR2     | Process alarm                                      | Input                    | BIT   |

|         | SysLim2PR2     | Process alarm                                      | Input                    | BIT   |

|         | Reg1Suicide    | Reg1 suicide relay status                          | Input                    | BIT   |

|         | :              | :                                                  | Input                    | BIT   |

|         | Reg4Suicide    | Reg4 suicide relay status                          | Input                    | BIT   |

|         | Reg1_PosAFIt   | Reg1, LM machine only, position A failure          | Input                    | BIT   |

|         | :              | :                                                  | Input                    | BIT   |

|         | Reg4_PosAFIt   | Reg4, LM machine only, position A failure          | Input                    | BIT   |

|         | Reg1_PosBFIt   | Reg1, LM machine only, position B failure          | Input                    | BIT   |

|         | :              | :                                                  | Input                    | BIT   |

|         | Reg4_PosBFIt   | Reg4, LM machine only, position B failure          | Input                    | BIT   |

|         | Reg1_PosDif1   | Reg1, LM machine only, position Diff failure       | Input                    | BIT   |

|         | :              | :                                                  | Input                    | BIT   |

|         | Reg4_PosDif1   | Reg4, LM machine only, position diff failure       | Input                    | BIT   |

|         | Reg1_PosDif2   | Reg1, LM machine only, position diff failure       | Input                    | BIT   |

|         | :              | :                                                  | Input                    | BIT   |

|         | Reg4_PosDif2   | Reg4, LM machine only, position diff failure       | Input                    | BIT   |

|         | RegCalMode     | Regulator under calibration                        | Input                    | BIT   |

|         | Reg1_Fdbk      | Regulator 1 feedback                               | Input                    | FLOAT |

|         | :              | :                                                  | Input                    | FLOAT |

|         | Reg4_Fdbk      | Regulator 4 feedback                               | Input                    | FLOAT |

|         | PilotFdbk1     | Pilot/Cyl                                          | Input                    | FLOAT |

|         |                |                                                    |                          |       |

| :                  | :                                                  | Input                     | FLOAT |

|--------------------|----------------------------------------------------|---------------------------|-------|

| PilotFdbk4         | Pilot/Cyl                                          | Input                     | FLOAT |

| Reg1_Error         | Null bias error Input                              | Input                     | FLOAT |

| :                  | :                                                  | Input                     | FLOAT |

| Reg4_Error         | Null bias error Input                              | Input                     | FLOAT |

| Accel1             | GPM/sec                                            | Input                     | FLOAT |

| Accel2             | GPM/sec                                            | Input                     | FLOAT |

| Mon1               | Position monitor                                   | Input                     | FLOAT |

| :                  | :                                                  | Input                     | FLOAT |

| Mon12              | Position monitor                                   | Input                     | FLOAT |

| CalibEnab1         | Enable calibration reg 1                           | Output                    | BIT   |

| :                  | :                                                  | Output                    | BIT   |

| CalibEnab4         | Enable calibration reg 4                           | Output                    | BIT   |

| SuicideForce1      | Force suicide reg 1                                | Output                    | BIT   |

| :                  | :                                                  | Output                    | BIT   |

| SuicideForce4      | Force suicide reg 4                                | Output                    | BIT   |

| PossDiffEnab1      | Position difference enable reg 1, LM only          | Output                    | BIT   |

| :                  | :                                                  | Output                    | BIT   |

| PossDiffEnab4      | Position difference enable reg 4, LM only          | Output                    | BIT   |

| Reg1_Ref           | Reg 1 position ref                                 | Output                    | FLOAT |

| :                  | :                                                  | Output                    | FLOAT |

| Reg4_Ref           | Reg 4 position ref                                 | Output                    | FLOAT |

| Reg1-GainMod       | Reg 1 gain modifier                                | Output                    | FLOAT |

| :                  | :                                                  | Output                    | FLOAT |

| Reg4-GainMod       | Reg 4 gain modifier                                | Output                    | FLOAT |

| Reg1_NullCor       | Reg 1 null bias correction                         | Output                    | FLOAT |

| :                  | :                                                  | Output                    | FLOAT |

| Reg4_NullCor       | Reg 4 null bias correction                         | Output                    | FLOAT |

| Internal Variables | Internal variables to service the auto-calibration | display, not configurable |       |

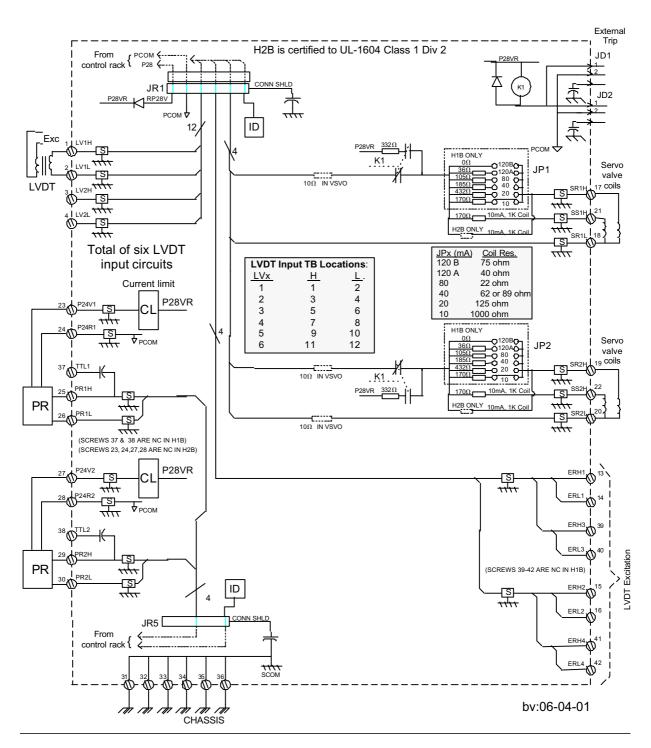

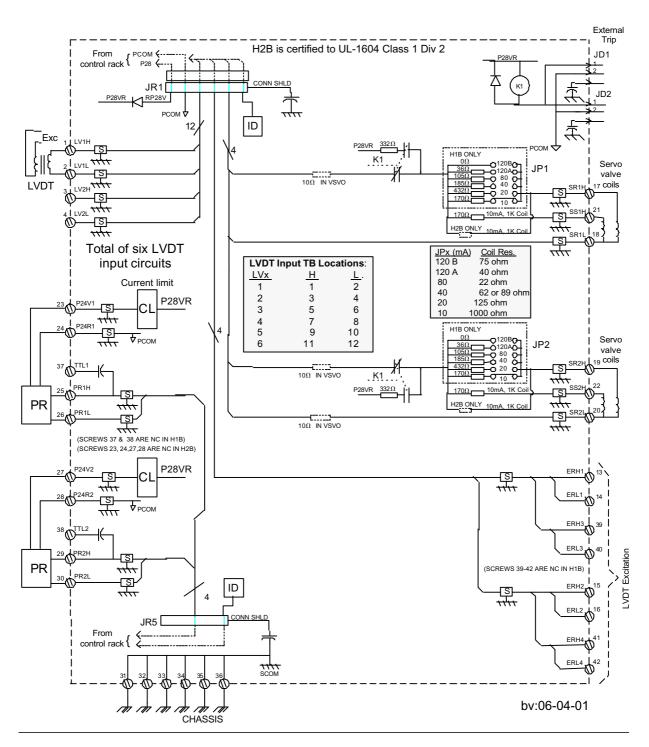

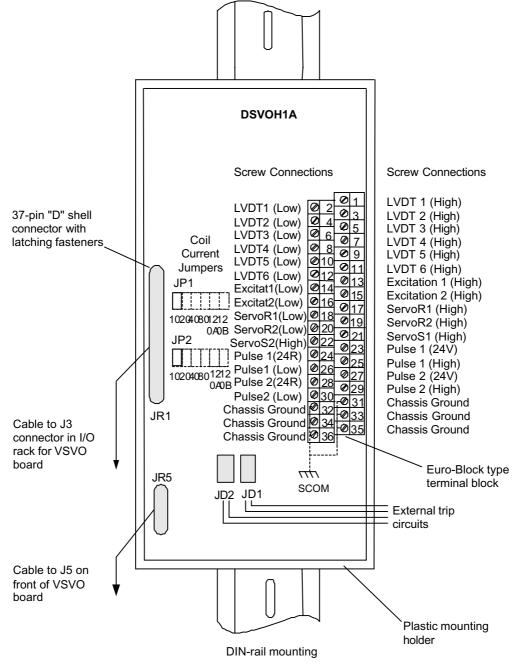

## DSVO–Simplex DIN-rail Mounted Servo Terminal Board

The DSVO board is a compact servo terminal board, designed for DIN\_rail mounting. This board has two servo outputs, I/O for six LVDT position sensors, and two active pulse rate inputs for flow measurement (refer to the diagrams). Servo coil currents ranging from 10 to 120 mA can be jumper selected. DSVO connects to the VSVO processor board with a 37-pin cable, which are identical to those used on the larger TSVO board. The terminal boards can be stacked vertically on the DIN-rail to conserve cabinet space. Two DSVO boards can be connected to the VSVO, if required. Only the Simplex version of this board is available

The on-board functions and high frequency decoupling to ground are the same as those on the TSVO. High density Euro-Block type terminal blocks are permanently mounted to the board with six screws for the ground connection (SCOM). Each of

the two connectors, JR1 and J5, connect to signals from on-board ID chips which identify the board to the VSVO for system diagnostic purposes.

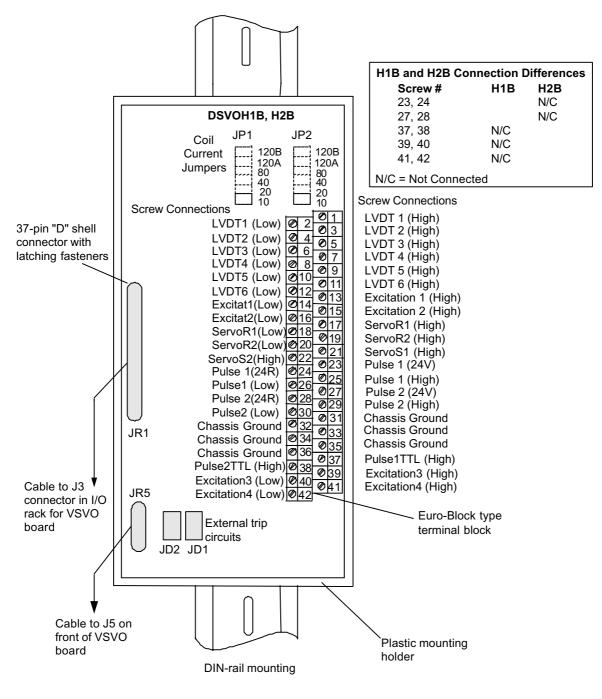

There are versions of the DSVO, H1B and H2B. The H1B is a direct replacement for the previous H1A design. The H2B is certified by UL as Class 1 Division 2.

The differences between the H1B and H1B versions of DSVO are as follows:

| Function                                     | H1B                                 | H2B                  |

|----------------------------------------------|-------------------------------------|----------------------|

| Class 1, Div. 2 certification                | No                                  | Yes                  |

| Servo valves<br>accommodated                 | 75, 40, 22, 62, 89, 125,<br>1k ohms | 1k ohms (10 mA)      |

| LVDT excitation outputs                      | Qty. = 2, 120 mA each               | Qty. = 4, 60 mA each |

| Excitation for pulse rate probes             | Qty. = 2, 24 V dc, 100<br>mA each   | No                   |

| Additional pulse rate inputs for TTL signals | No                                  | Qty. = 2             |

DSVOH1A Board

#### Mark VI Servo Valve Terminal Board IS200DSVOH1B, H2B

(IS200DSVOH1B Replaces IS200DSVOH1A)

DSVOH1B, H2B Board (Part 1 of 2)

#### Mark VI Servo Valve Terminal Board IS200DSVOH1B, H2B

(IS200DSVOH1B Replaces IS200DSVOH1A)

DSVOH1B, H2B board (Part 2 of 2)

#### Installation

There is no shield termination strip with this design.

The DSVO board slides into a plastic holder, which mounts on the DIN-rail. The servo I/O are wired directly to the Euro-Block type terminal block as shown in the following figures. This has 36 terminals (DSVOH1A) or 42 terminals (DSVOH1B, H2B); typically #18 AWG shielded twisted pair wiring is used. There are six screws for SCOM (ground) connection, which should be as short as distance as possible.

DSVIH1A Wiring and Cabling

DSVOH1B, H2B Wiring and Cabling

# I/O Board Alarms

\_

Diagnostic alarms for any I/O board can be displayed and reset from the toolbox. For troubleshooting and general diagnostic alarm information refer to GEH-6421 Volume I, Chapter 8.

#### I/O Board Diagnostic Alarms

| Board | Fault | Fault Description                                                                                                                                                                    | Possible Cause                                                                                                                                                       |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vsvo  | 2     | Flash Memory CRC Failure                                                                                                                                                             | Board firmware programming error<br>(board will not go online)                                                                                                       |

|       | 3     | CRC failure override is Active                                                                                                                                                       | Board firmware programming error (board is allowed to go online)                                                                                                     |

|       | 16    | System Limit Checking is Disabled                                                                                                                                                    | System checking was disabled by configuration.                                                                                                                       |

|       | 17    | Board ID Failure                                                                                                                                                                     | Failed ID chip on the VME I/O board                                                                                                                                  |

|       | 18    | J3 ID Failure                                                                                                                                                                        | Failed ID chip on connector J3, or cable problem                                                                                                                     |

|       | 19    | J4 ID Failure                                                                                                                                                                        | Failed ID chip on connector J4, or cable problem                                                                                                                     |

|       | 20    | J5 ID Failure                                                                                                                                                                        | Failed ID chip on connector J5, or cable problem                                                                                                                     |

|       | 21    | J6 ID Failure                                                                                                                                                                        | Failed ID chip on connector J6, or<br>cable problem                                                                                                                  |

|       | 22    | J3A ID Failure                                                                                                                                                                       | Failed ID chip on connector J3A, or cable problem                                                                                                                    |

|       | 23    | J4A ID Failure                                                                                                                                                                       | Failed ID chip on connector J4A, or cable problem                                                                                                                    |

|       | 24    | Firmware/Hardware Incompatibility                                                                                                                                                    | Invalid terminal board connected to VME I/O board                                                                                                                    |

|       | 30    | ConfigCompatCode mismatch; Firmware: #; Tre: #<br>The configuration compatibility code that the firmware is<br>expecting is different than what is in the tre file for this<br>board | A tre file has been installed that is<br>incompatible with the firmware on the<br>I/O board. Either the tre file or<br>firmware must change. Contact the<br>factory. |

|       | 31    | IOCompatCode mismatch; Firmware: #; Tre: #<br>The I/O compatibility code that the firmware is expecting<br>is different than what is in the tre file for this board                  | A tre file has been installed that is<br>incompatible with the firmware on the<br>I/O board. Either the tre file or<br>firmware must change. Contact the<br>factory. |

|       | 33-44 | LVDT # RMS Voltage Out of Limits. Minimum and<br>maximum LVDT limits are configured                                                                                                  | The LVDT may need recalibration.                                                                                                                                     |

|       | 45    | Calibration Mode Enabled                                                                                                                                                             | The VSVO was put into calibration mode.                                                                                                                              |

|       | 46    | VSVO Board Not Online, Servos Suicided. The servo is suicided because the VSVO is not on-line                                                                                        | The controller (R, S, T) or IONet is<br>down, or there is a configuration<br>problem with the system preventing<br>the VCMI from bringing the board on<br>line.      |

| 47-51   | Servo Current # Disagrees with Reference, Suicided.<br>The servo current error (reference - feedback) is greater<br>than the configured current suicide margin          | A cable/wiring open circuit, or board problem.                                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 52-56   | Servo Current # Short Circuit. This is not currently used                                                                                                               | NA                                                                                                                             |

| 57-61   | Servo Current # Open Circuit. The servo voltage is greater than 5V and the measured current is less than 10%                                                            | A cable/wiring open circuit, or board problem.                                                                                 |

| 62-66   | Servo Position # Feedback Out of Range, Suicided.<br>Regulator number # position feedback is out of range,<br>causing the servo to suicide                              | LVDT or board problem                                                                                                          |

| 67-71   | Configuration Message Error for Regulator Number #.<br>There is a problem with the VSVO configuration and the<br>servo will not operate properly                        | The LVDT minimum and maximum voltages are equal or reversed, or an invalid LVDT, regulator, or servo number is specified.      |

| 72      | Onboard Calibration Voltage Range Fault. The A/D calibration voltages read from the FPGA are out of limits, and the VSVO will use default values instead                | A problem with the Field<br>Programmable Gate Array (FPGA) on<br>the board                                                     |

| 73-75   | LVDT Excitation # Voltage out of range                                                                                                                                  | There is a problem with the LVDT excitation source on the VSVO board.                                                          |

| 77      | Servo output assignment mismatch. Regulator types 8 & 9 use two servo outputs each. They have to be consecutive pairs, and they have to be configured as the same range | Fix the regulator configurations.                                                                                              |

| 128-191 | Logic Signal # Voting mismatch. The identified signal from this board disagrees with the voted value                                                                    | A problem with the input. This could<br>be the device, the wire to the terminal<br>board, the terminal board, or the<br>cable. |

| 224-259 | Input Signal # Voting mismatch, Local #, Voted #. The specified input signal varies from the voted value of the signal by more than the TMR Diff Limit                  | A problem with the input. This could<br>be the device, the wire to the terminal<br>board, the terminal board, or the<br>cable. |

+1 540 387 7000 www. Geindustrial.com

GE Industrial Systems

General Electric Company 1501 Roanoke Blvd. Salem, VA 24153-6492 USA

## **GE Industrial Systems**

# VTUR Turbine Control Board

These instructions do not purport to cover all details or variations in equipment, nor to provide for every possible contingency to be met during installation, operation, and maintenance. The information is supplied for informational purposes only, and GE makes no warranty as to the accuracy of the information included herein. Changes, modifications, and/or improvements to equipment and specifications are made periodically and these changes may or may not be reflected herein. It is understood that GE may make changes, modifications, or improvements to the equipment referenced herein or to the document itself at any time. This document is intended for trained personnel familiar with the GE products referenced herein.

GE may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not provide any license whatsoever to any of these patents. All license inquiries should be directed to the address below. If further information is desired, or if particular problems arise that are not covered sufficiently for the purchaser's purpose, the matter should be referred to:

GE Industrial Systems Post Sales Service 1501 Roanoke Blvd. Salem, VA 24153-6492 USA Phone: + 1 888 GE4 SERV (888 434 7378, United States) + 1 540 378 3280 (International) Fax: + 1 540 387 8606 (All)

("+" indicates the international access code required when calling from outside the USA)

This document contains proprietary information of General Electric Company, USA and is furnished to its customer solely to assist that customer in the installation, testing, operation, and/or maintenance of the equipment described. This document shall not be reproduced in whole or in part nor shall its contents be disclosed to any third party without the written approval of GE Industrial Systems.

GE PROVIDES THE FOLLOWING DOCUMENT AND THE INFORMATION INCLUDED THEREIN AS IS AND WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED STATUTORY WARRANTY OF MERCHANTABILITY OR FITNESS FOR PARTICULAR PURPOSE.

Issue date: 2002-06-30

© 2002 by General Electric Company, USA. All rights reserved.

| Section                          | Page |

|----------------------------------|------|

| Functional Description           | 2    |

| Installation                     |      |

| Operation                        | 6    |

| Features                         |      |

| Specifications                   |      |

| Diagnostics                      | 9    |

| Automatic Synchronizing          |      |

| Configuration                    | 12   |

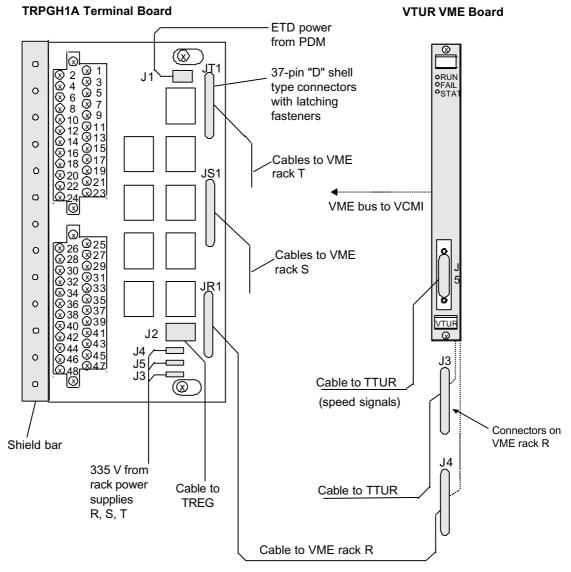

| TRPG Primary Trip Terminal Board | 15   |

| Installation                     | 16   |

| Operation                        |      |

| Features                         |      |

| Diagnostics                      |      |

| Configuration                    |      |

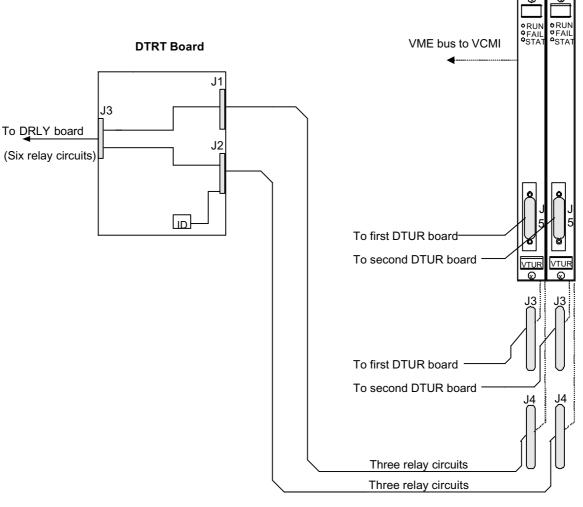

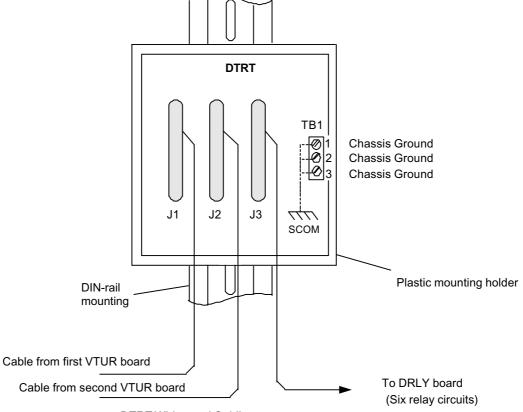

| DTRT Trip Transition Board       |      |

| Installation                     | 21   |

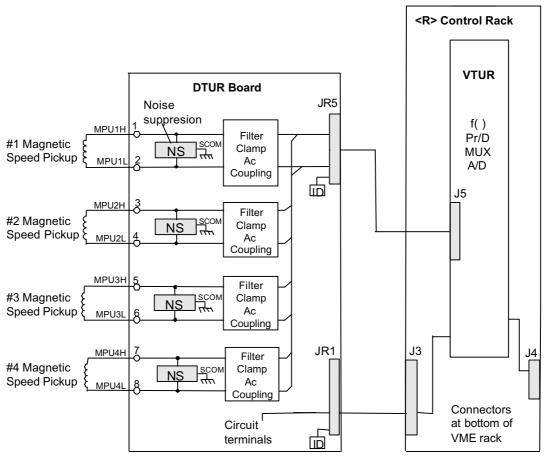

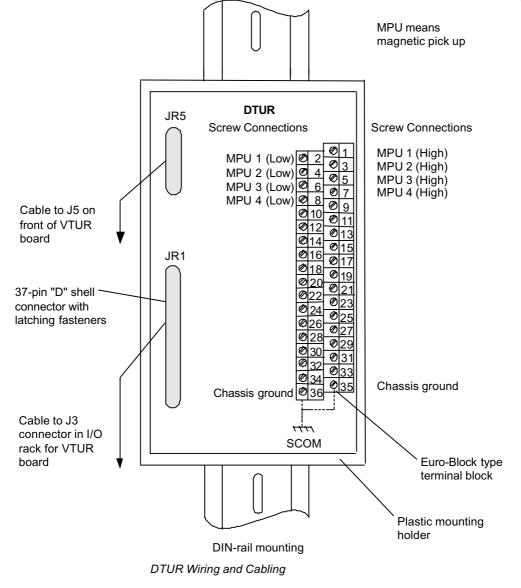

| DTUR Pulse Rate Terminal Board   | 22   |

| Installation                     | 23   |

| I/O Board Alarms                 | 24   |

# **Functional Description**

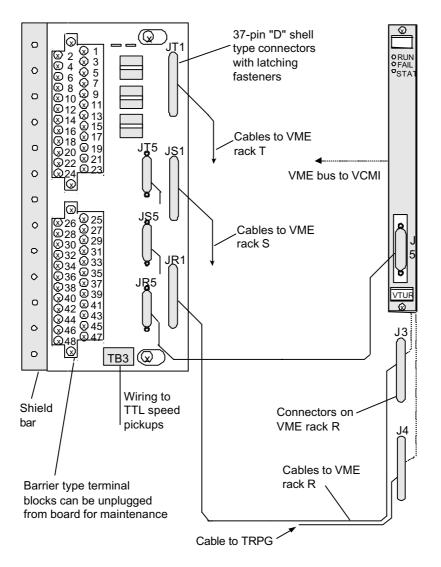

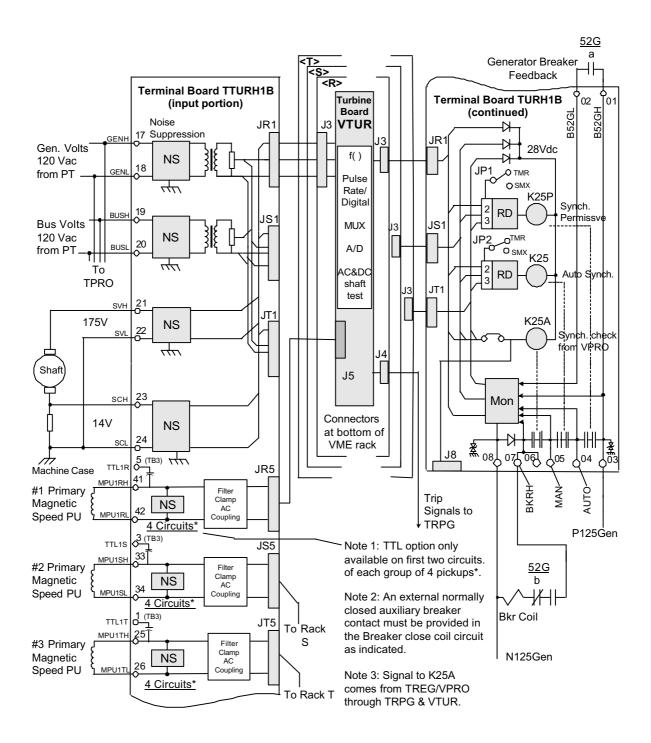

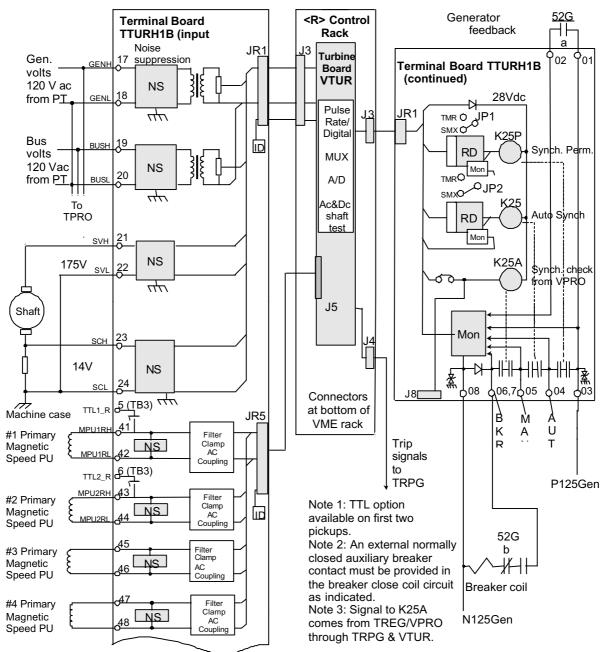

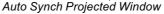

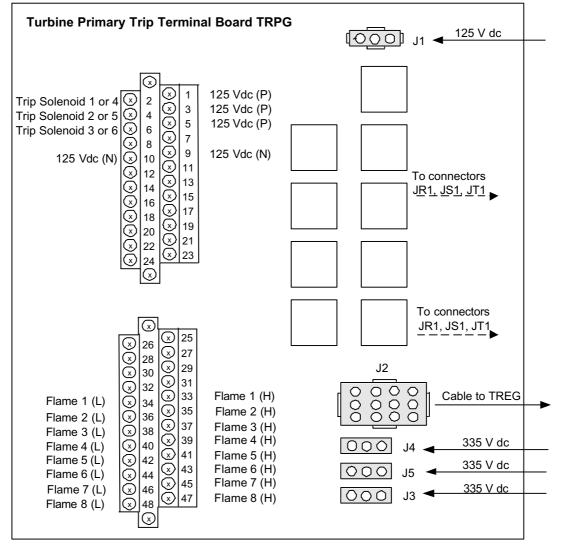

The turbine control board, VTUR controls three primary overspeed trip solenoids and automatic synchronizing. It also interfaces to four passive pulse rate devices, and monitors shaft voltage and current. The speed signal cable to VTUR uses the J5 plug on the front of the board, and the other signals use the J3 connector on the VME rack. Terminal board TTUR provides simplex signals through the JR connector, and fans out TMR signals to the JR, JS, and JT connectors. J4 on the VME rack connects to the TRPG terminal board described in the Primary Trip section.

A two-slot version of this board (VTURH2) is available for driving six trip solenoids using two TRPG boards. VTURH2 only accepts eight flame detectors.

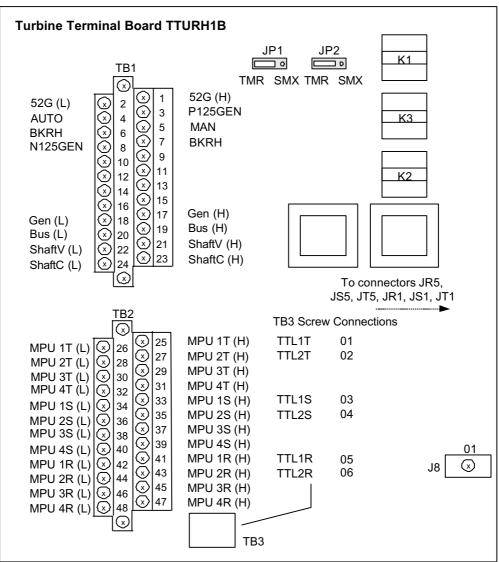

#### **TTURH1B Terminal Board**

#### **VTUR VME Board**

Turbine Control Terminal Board, Processor Board, and Cabling

### Installation

Magnetic pick ups, shaft pick ups, potential transformers, and breaker relays are wired to two I/O terminal blocks on TTUR. Each block is held down with two screws and has 24 terminals accepting up to #12 AWG wires. A shield termination strip attached to chassis ground is located immediately to the left of each terminal block. Jumpers JP1 and JP2 select either SMX or TMR for relay drivers K25 and K25P. TB3 is for optional TTL connections to active speed pickups; these require an external power supply.

TTUR Terminal Board

All three relays have two normally open contacts in series with the breaker close coil. In TMR applications all inputs fan to the three control racks. Control signals coming into TTUR from R, S, and T are voted before they actuate permissive relays K25 and K25P. Relay K25A is controlled by the VPRO and TREG boards.

Turbine Control Inputs, Synchronizing, and Primary Trip Interface, TMR

# Operation

Pulse rate to digital circuits are on the VTUR board. VTUR alarms high voltages and tests the integrity and continuity of the circuitry. In the simplex application, up to four pulse rate signals may be used to measure turbine speed. Generator and bus voltages are brought into VTUR for automatic synchronizing in conjunction with the turbine controllerand excitation system. TTUR has permissive generator synchronizing relays and controls the main breaker relay coil 52G. Shaft voltage is picked up with brushes and monitored along with the current to the machine case.

Turbine Control Inputs, Synchronizing, and Primary Trip Interface, Simplex

### Features

The median speed signal is used for speed control and for the primary overspeed trip signal.

A metal oxide varister (MOV) and a current limiting resistor are used in each circuit. An interface is provided for four passive, magnetic speed inputs with a frequency range of 2 - 20,000 Hz. Using passive pickups on a 60-tooth wheel, circuit sensitivity allows detection of 2 rpm turning gear speed to determine if the turbine is stopped (zero speed). If automatic turning gear engagement is provided in the turbine control, this signal initiates turning gear operation.

The primary overspeed trip calculations are performed in the controllerusing algorithms similar to (but not the same as) those shown in the section on the VPRO Protection Module. The fast trip option used on gas turbines runs in VTUR and is described below.

The normal primary overspeed trip is calculated in the controller and passed to the VTUR and then to the TRPG terminal board. TRPG contains magnetic relays for interface with the electrical trip devices (ETDs). TRPG works in conjunction with the TREG board to form the *Primary* and *Emergency* sides of the interface to the ETDs. Usually this applies to turbines which do not have a mechanical overspeed bolt and require a separate emergency overspeed (EOS) system. Three ETDs can be driven from each TRPG/TREG combination with the positive side of each solenoid connected to the TREG and the negative side connected to the TRPG.

Two different versions of the TRPG are available, with version 1 used for triple redundant (TMR) systems and version 2 used for Simplex systems. The only difference is that the TMR version has three voting relays per ETD circuit and the Simplex version has one relay per circuit. The VTUR board monitors the current flowing in its relay driver control line to determine its energize or de-energize vote/status of the relay coil. A normally closed contact from each relay on the TRPG board is monitored by the diagnostics to determine its proper operation.

Bearings can be damaged by the flow of electrical current from the shaft to the case. This current can occur for several reasons.

- A static voltage can be caused by droplets of water being thrown off the last stage buckets in a steam turbine. This voltage will build up until a discharge occurs through the bearing oil film.

- An ac ripple on the dc generator field can produce an ac voltage on the shaft with respect to ground through the capacitance of the field winding and insulation. Note that both of these sources are weak, so high impedance instrumentation is used to measure these voltages with respect to ground.

- A voltage may be generated between the ends of the generator shaft due to dissymmetries in the generator magnetic circuits. If the insulated bearings on the generator shaft break down, the current will flow from one end of the shaft through the bearings and frame to the other end. Brushes can be used to discharge damaging voltage buildup, and a shunt should be used to monitor the current flow.

The turbine control continuously monitors the shaft to ground voltage and current, and alarms excessive levels. There is an ac test mode and a dc test mode. The ac test applies an ac voltage to test the integrity of the measuring circuit.

The dc test checks the continuity of the external circuit, including the brushes, turbine shaft, and the interconnecting wire.

**Note** The dc test is driven from the <R> controller only. If the <R> controller is down, this test cannot be run successfully.

# Specifications

| Item                                       | Specification                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of inputs                           | TTUR: 12 passive speed pickups<br>1 shaft voltage and 1 shaft current measurement<br>1 generator and 1 bus voltage<br>Generator breaker status contact                                                                                                                                                                                                             |

|                                            | VTUR: 4 passive speed pickups<br>1 shaft voltage and 1 current measurement<br>1 generator and 1 bus voltage<br>Generator breaker status<br>8 flame detectors from first TRPG                                                                                                                                                                                       |

| Number of outputs                          | TTUR: Generator breaker coil, 5A at 125 V dc                                                                                                                                                                                                                                                                                                                       |

|                                            | VTUR: Automatic synchronizing<br>Primary trip solenoid interface, 3 outputs to TRPG<br>Additional 3 trip outputs from second TRPG using VTURH2                                                                                                                                                                                                                     |

| Trip solenoids (TRPG)                      | Solenoids draw up to 1 A at 125 V dc and have a time constant of $L/R = 0.1$ sec.                                                                                                                                                                                                                                                                                  |

| Power supply voltage                       | TTUR: Nominal 125 V dc to breaker coil                                                                                                                                                                                                                                                                                                                             |

| MPU pulse rate range                       | 2 Hz to 20 kHz                                                                                                                                                                                                                                                                                                                                                     |

| MPU pulse rate accuracy                    | 0.05% of reading                                                                                                                                                                                                                                                                                                                                                   |

| MPU input circuit sensitivity              | 27 mV pk (detects 2 rpm speed)                                                                                                                                                                                                                                                                                                                                     |

| Shaft voltage monitor                      | Signal is frequency of $\pm$ 5 V dc (0 – 1 MHz) pulses from 0 to 2,000 Hz                                                                                                                                                                                                                                                                                          |

| Shaft voltage wiring                       | Up to 300 m (984 ft), with maximum two-way cable resistance of 15 ohms                                                                                                                                                                                                                                                                                             |

| Shaft voltage dc test                      | Applies a 5 V dc source to test integrity of the external turbine circuit and measures dc current flow. Circuit computes a differential resistance between 0 and 150 ohms within $\pm$ 5 ohms and compares against shunt limit and brush limit. Readings above 50 ohms indicate a fault. Return signal is filtered to provide 40 dB of noise attenuation at 60 Hz. |

| Shaft voltage ac test                      | Applies a test voltage of 1 kHz to the input of the VTUR shaft voltage circuit (R module only). Shaft voltage monitor circuit on R, S, and T displays an offset of 1000 Hz from normal reading.                                                                                                                                                                    |

| Shaft current input                        | Measures shaft current in amps ac (shunt voltage up to 0.1 V pp)                                                                                                                                                                                                                                                                                                   |

| Generator and bus voltage sensors          | Two single phase potential transformers, with secondary output supplying a<br>nominal 115 V rms<br>Each input has less than 3 VA of loading.<br>Allowable voltage range for synch is 75 to 130 V rms.<br>Each PT input is magnetically isolated with a 1,500 V rms barrier.<br>Cable length can be up to 1,000 ft. of 18 AWG wiring.                               |

| Synchronizing measurements                 | Frequency accuracy 0.05% over 45 to 66 Hz range. Zero crossing of the inputs is monitored on the rising slope. Phase difference measurement is better than $\pm$ 1 degree.                                                                                                                                                                                         |

| Generator breaker circuits (synchronizing) | External circuits should have a voltage range within 20 to 140 V dc. The external circuit must include a NC breaker auxiliary contact to interrupt the current. Circuits are rated for NEMA class E creepage and clearance. 250 V dc applications require interposing relays.                                                                                      |

| Contact voltage sensing                    | 20 V dc indicates high and 6 V dc indicates low.<br>Each circuit is optically isolated and filtered for 4 ms.                                                                                                                                                                                                                                                      |

### Diagnostics

Diagnostic information includes feedback from the solenoid relay driver and contact, high flame detector voltage, slow synch check relay, slow auto synch relay, and locked up K25 relay. If any one of the signals goes unhealthy, a composite diagnostic alarm L3DIAG\_VTUR occurs. The diagnostic signals can be individually latched and then reset with the RESET\_DIA signal if they go healthy.

Terminal board connectors JR1, JS1, JT1, JR5, JS5, JT5 have their own ID device which is interrogated by the I/O board. The ID device is a read-only chip coded with the terminal board serial number, board type, revision number, and plug location.

### Automatic Synchronizing

All synchronizing connections are located on the TTUR terminal board. The generator and bus voltages are supplied by two, single phase, potential transformers (PTs) with a fused secondary output supplying a nominal 115 V rms. Measurement accuracy between the zero crossing for the bus and generator voltage circuits is 1 degree.

Turbine speed is matched against the bus frequency, and the generator and bus voltages are matched by adjusting the generator field excitation voltage from commands sent between the turbine controller and the EX2000 over the Unit Data Highway (UDH). A command is given to close the breaker when all permissives are satisfied, and the breaker is predicted to close within the calculated phase/slip window. Feedback of the actual breaker closing time is provided by a 52G/a contact from the generator breaker (not an auxiliary relay) to update the data base. An internal K25A synch check relay is provided on the TTUR; the independent backup phase/slip calculation for this relay is performed in the <P> Protection Module. Diagnostics monitor the relay coil and contact closures to determine if the relay properly energizes or de-energizes upon command.

#### Synchronizing Modes

There are three basic synchronizing modes. Traditionally, these modes are selected from a generator panel mounted selector switch:

- **Off** The breaker will not be closed by the Mark VI control. The check relay will not pickup.

- **Manual** The operator initiates breaker close, which is still subject to the K25A Synch Check contacts driven by VPRO. The manual close is initiated from an external contact on the generator panel, normally connected in series with a *Synch Mode in Manual* contact.

- Auto The system will automatically match voltage and speed, and then close the breaker at the right time to hit top dead center on the synchroscope. All three of the following functions must agree for this closure to occur:

- **K25A** synch check relay, checks the allowable slip/phase window, from VPRO.

- **K25** auto synch relay, provides precision synchronization, from VTUR.

- **K25P** synch sequence permissive, checks the turbine sequence status, from VTUR.

Details of the various checks are discussed in the following sections.

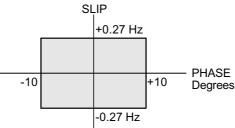

#### Synch Check

The K25A synch check function is based on phase lock loop techniques. The calculations for this function are done in the VPRO, but interfaces to the Breaker close circuit on the TTUR board. It performs limit checks against adjustable constants as follows:

- Generator undervoltage

- Bus undervoltage

- Voltage error

- Frequency error (slip), with a maximum value of 0.33 Hz, typically set to 0.27 Hz

- Phase error with a maximum value of 30 degrees, typically set to 10 degrees

In addition, synch check arms logic to enable the function and provides bypass logic for deadbus closure. The synch window is based on typical settings:

Typical Synch Window

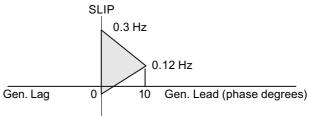

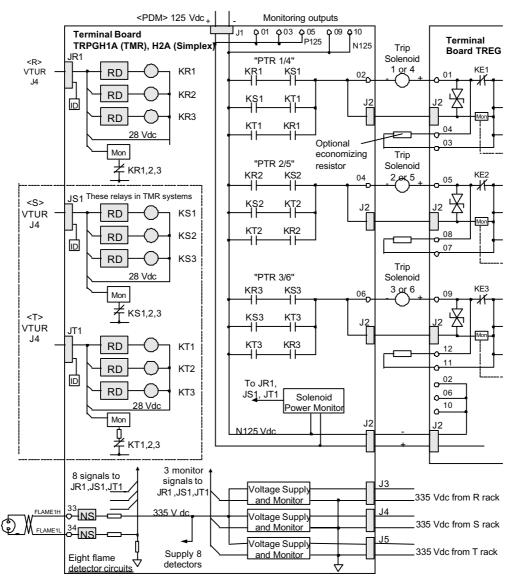

#### Auto Synch

The Auto Synch K25 function uses zero voltage crossing techniques. It compensates for the breaker time delay, which is defined by two adjustable constants with logic selection between the two (for two breaker applications). The calculations, which are done on the VTUR board, include phase, slip, acceleration, and anticipated time lead for the breaker delay. Based on the measured breaker close time, the time delay parameter is adjusted, up to certain limits.

In addition, auto synch arms logic to enable the function and bypasses logic to provide for deadbus or manual closure. The auto synch projected synch window is where positive slip indicates the generator frequency is higher than the bus frequency.

The projected window is based on current phase, current slip, and current acceleration. The generator must currently be lagging and have been lagging for the last 10 consecutive cycles, and projected (anticipated) to be leading when the breaker actually reaches closure. Auto synch will not allow the breaker to close with negative slip; speed matching typically aims at around +0.12 Hz slip.

#### Synchronization Display

A special synchronization screen is available on the HMI with a real-time graphical phase display and control pushbuttons. The display items are listed in the following table.

| Synch Display       | Description                                                                                                                                                      |                                                                                                                                                                                          |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dynamic parameters  | Voltages:<br>Frequencies:<br>Phase:                                                                                                                              | Generator, bus, difference<br>Generator, bus, slip (difference)<br>Difference angle, degrees                                                                                             |

| Status indication   | Mode: Synch OFF, M<br>Synch monitor:<br>Dead bus breaker:<br>Second breaker if ap<br>Synch permissive:<br>Auto synch enabled<br>Speed adjust:<br>Voltage adjust: | OFF, ON<br>Open/close                                                                                                                                                                    |

| Synch permissives   | Generator voltage:<br>Bus voltage:<br>Generator frequency:<br>Bus frequency:<br>Difference volts:<br>Difference frequency:<br>Phase:K25<br>K25A                  | OK/not OK<br>OK/not OK                                                                                                                                                                   |

| Limit constants     | Upper and lower limit                                                                                                                                            | s for the above permissives                                                                                                                                                              |

| Breaker performance | Diagnostics:                                                                                                                                                     | Slow check relay<br>Synch relay lockup<br>Breaker #1 close time out of limits<br>Breaker #2 close time out of limits<br>Relay K25P trouble<br>Breaker closing voltage (125 V dc) missing |

| Control pushbuttons | Synch monitor:<br>Speed adjust: RAISE<br>Voltage adjust:                                                                                                         | ON, OFF<br>, LOWER<br>RAISE, LOWER                                                                                                                                                       |

Synchronizing Display Items

# Configuration

The following table defines the configuration choices and defaults. For details refer to GEH-6403, *Control System Toolbox for Configuring the Mark VI Turbine Controller. Typical VTUR Configuration*

| Parameter          | Description                              | Choices                          |

|--------------------|------------------------------------------|----------------------------------|

| Configuration      |                                          |                                  |

| VTUR system limits | Select system limits                     | Enable, disable                  |

| SMredundancy       | Select Simplex or TMR system             | Simplex or TMR                   |

| AccelCalType       | Select acceleration calculation type     | Slow, medium, fast               |

| FastTripType       | Select Fast Trip algorithm               | Unused, PR_Single, PR_Max        |

| J3J5:IS200TTURH1A  | TTUR connected to VTUR through J3 and J5 | Connected, not connected         |

| PulseRate1         | Pulse rate input 1 - board point         | Point edit (input FLOAT)         |

| PRType             | Select Speed or Flow type input          | Unused, speed, flow,<br>Speed_LM |

| PRScale            | Select pulses per revolution             | 0 to 1,000                       |

| SysLim1Enable      | Select system limit 1                    | Enable, disable                  |

| SysLim1Latch       | Select whether alarm will latch          | Latch, not latch                 |

| SysLim1Type        | Select type of alarm initiation          | >= or <=                         |

| SysLimit1          | Select alarm level in GPM or RPM         | 0 to 20,000                      |

| SysLim2Enable      | Select system limit 2 (as above)         | Enable, disable                  |

| TMRDiffLimit       | Difference limit for voted PR inputs EU  | 0 to 20,000                      |

| ShVoltMon          | Shaft voltage monitor - board point      | Point edit (input FLOAT)         |

| SysLim1Enable      | Select System Limit 1                    | Enable, disable                  |

| SysLim1Latch       | Select whether alarm will latch          | Latch, not latch                 |

| SysLim1Type        | Select type of alarm initiation          | >= or <=                         |

| SysLimit1          | Select alarm level in frequency          | 0 to 100                         |

| SysLim2Enable      | Select system limit 2 (as above)         | Enable, disable                  |

| ShCurrMon          | Shaft current monitor - board point      | Point edit (input FLOAT)         |

| ShuntOhms          | Shunt resistance                         | 0 to 100                         |

| Shunt limit        | Shunt maximum ohms                       | 0 to 100                         |

| Brush limit        | Shaft brush maximum ohms                 | 0 to 100                         |

| SysLim1Enable      | Select system limit 1                    | Enable, disable                  |

| SysLim1Latch       | Select whether alarm will latch          | Latch, not latch                 |

| SysLim1Type        | Select type of alarm initiation          | >= or <=                         |

| SysLimit1          | Select alarm level in amps               | 0 to 100                         |

|              | SysLim2Enable    | Select system limit 2                                       | Enable, disable          |      |

|--------------|------------------|-------------------------------------------------------------|--------------------------|------|

| GenPT_KVolts |                  | Generator potential transfomer - board point Point edit (ir |                          | OAT) |

| PT_Input     |                  | PT input in kVrms for PT output                             | 0 to 1,000               |      |

| PT_Output    |                  | PT output in Vrms, nominal 115 V rms                        | 0 to 150                 |      |

|              | SysLim1          | Select alarm level in kVrms                                 | 0 to 1,000               |      |

|              | SysLim2          | Select alarm level in kVrms                                 | 0 to 1,000               |      |

|              | BusPT_Kvolts     | Bus potential transformer - board point                     | Point edit (input FL     | OAT) |

|              | Ckt_Bkr          | Circuit breaker - board point                               | Point edit (input BIT)   |      |

|              | System Frequency | Select frequency in Hz                                      | 50 or 60                 |      |

|              | CB1CloseTime     | Breaker 1 closing time, ms                                  | 0 to 1,000               |      |

|              | CB1 AdaptLimit   | Breaker 1 self adaptive limit, ms                           | 0 to 1,000               |      |

|              | CB1 AdaptEnabl   | Select breaker 1 self adaptive limit                        | Enable, disable          |      |

|              | CB1FreqDiff      | Breaker 1 special window frequency difference, Hz           | 0 to 10                  |      |

|              | CB1PhaseDiff     | Breaker 1 special window phase difference, degrees          | 0 to 30                  |      |

|              | CB2CloseTime     | Breaker 2 closing time, ms (as above)                       | 0 to 1,000               |      |

| J4:IS        | 200TRPGH1A       | TRPG terminal board, 8 flame detectors                      | Connected, not connected |      |

| Boar         | d Points Signals | Description – Point Edit (Enter Signal Connection)          | Direction                | Туре |

|              | L3DIAG_VTUR1     | Board diagnostic                                            | Input                    | BIT  |

|              | L3DIAG_VTUR2     | Board diagnostic                                            | Input                    | BIT  |

|              | L3DIAG_VTUR3     | Board diagnostic                                            | Input                    | BIT  |

|              | ShShntTst_OK     | Shaft voltage monitor shunt test OK                         | Input                    | BIT  |

|              | ShBrshTst_OK     | Shaft voltage brush test OK                                 | Input                    | BIT  |

|              | CB_Volts_OK      | L3BKR_VLT circuit breaker coil voltage available            | Input                    | BIT  |

|              | CB_K25P_PU       | L3BKR_PERM sync permissive relay picked up                  | Input                    | BIT  |

|              | CB_K25_PU        | L3KBR_GES auto sync relay picked up                         | Input                    | BIT  |

|              | CB_K25A_PU       | L3KBR_GEX sync check relay picked up                        | Input                    | BIT  |

|              | Gen_Sync_LO      | Generator sync trouble (lockout)                            | Input                    | BIT  |

|              | L25_Command      |                                                             | Input                    | BIT  |

|              | Kq1_Status       |                                                             | Input                    | BIT  |

|              | :                | :                                                           | Input                    | BIT  |

|              | Kq6_Status       |                                                             | Input                    | BIT  |

|              | FD1_Flame        |                                                             | Input                    | BIT  |

|              | :                | :                                                           | Input                    | BIT  |

|              | FD16_Flame       |                                                             | Input                    | BIT  |

|              | SysLim1PR1       |                                                             | Input                    | BIT  |

|              | :                | :                                                           | Input                    | BIT  |

|              | SysLim1PR4       |                                                             | Input                    | BIT  |

| SysLim1SHCAc shaft current high L30TSCHInputBITSysLim1GENInputBITSysLim1BUSInputBITSysLim2PR1(same set as for Limit1 above)InputBITGenFreqHz frequencyInputFLOATBusFreqHz frequencyInputFLOATGenVoltsDiffKiloVolts rms-GenLow is negativeInputFLOATGen Freq DiffSlip Hz-GenSlow is negativeInputFLOATGen Prase DiffPhase Degrees-Gen Lag is negativeInputFLOATCB1CloseTimeBreaker #1 close time in millisecondsInputFLOATCB2CloseTimeBreaker #2 close time in millisecondsInputFLOATCB2CloseTimeBreaker #2 close time in millisecondsInputFLOATAccel4RPM/SECInputFLOATFimDetPwr1335 V dcInputFLOATShTestDCL97SHAFT_AC SVM_AC_TESTOutputBITShTestDCL97SHAFT_DC SVM_DC_TESTOutputBITFD16_Level1 = high detection counts levelOutputBITSync_Perm_ASL83AS - auto sync permissiveOutputBITSync_MonitorL83S_MTR - monitor modeOutputBITSync_ResetL43AUT2 - 2nd breaker selectedOutputBITSync_ResetL86MR_SYNC - sync trouble resetOutputBITSync_ResetL86MR_SYNC - sync trouble resetOutputBITSync_ResetL86MR_SYNC - sync trouble reset                                                                         | SysLim1SHV     | Ac shaft voltage frequency high L30TSVH | Input  | BIT   |