| Section                                                  | Page |

|----------------------------------------------------------|------|

| Functional Description                                   | 2    |

| Installation                                             |      |

| Operation                                                | 6    |

| Control of Trip Solenoids                                | 6    |

| Solenoid Trip Tests                                      |      |

| Specifications                                           | 7    |

| Diagnostics                                              | 8    |

| Configuration                                            | 8    |

| TRPL/TREL Large Steam Turbine Primary and Emergency Trip | 9    |

| Features                                                 | 11   |

| Configuration                                            | 11   |

| Installation                                             | 14   |

| TRPS/TRES Small/Medium Steam Turbine Primary Trip        | 16   |

| Features                                                 | 16   |

| Configuration                                            | 16   |

| Installation                                             |      |

| TPRO Turbine Protection Terminal Board                   | 21   |

| Installation                                             | 24   |

| Operation                                                |      |

| Features                                                 | 25   |

| Specifications                                           |      |

| Diagnostics                                              | 27   |

| Configuration                                            |      |

| I/O Board Alarms                                         |      |

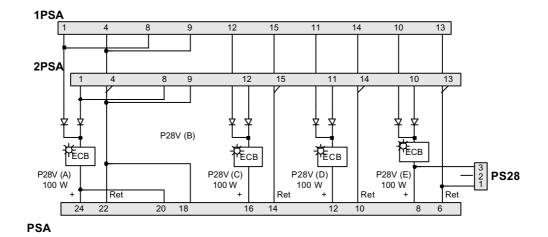

## **Functional Description**

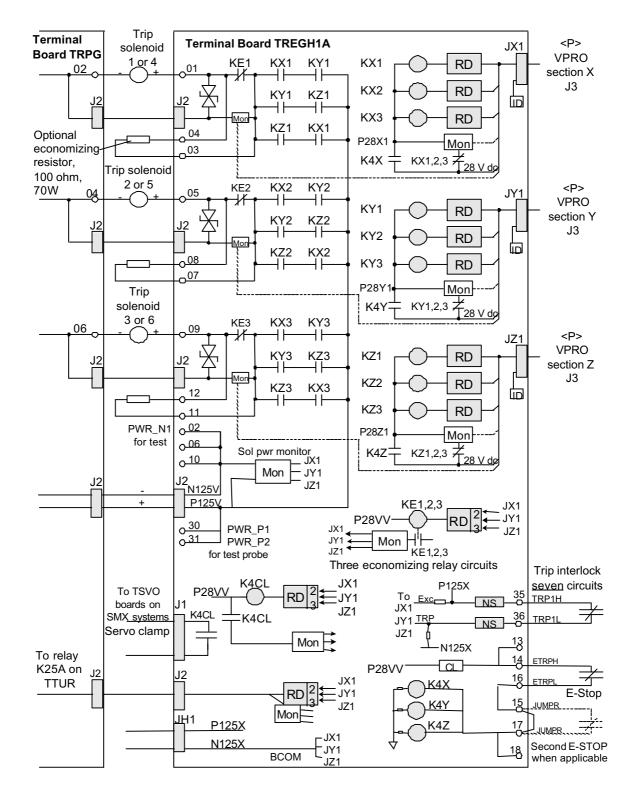

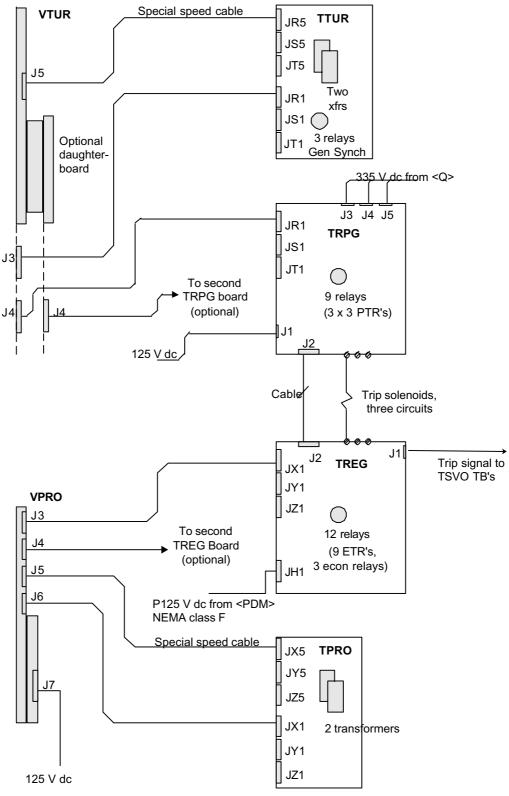

VPRO also connects to the TPRO terminal board and has an Ethernet connection for IONet communications with the control modules. The VPRO board in the Protection Module <P> provides the emergency trip function. Up to three trip solenoids can be connected between the TREG and TRPG terminal boards. TREG provides the positive side of the 125 V dc to the solenoids and TRPG provides the negative side. VPRO provides emergency overspeed protection and the emergency stop functions. It controls the 12 relays on TREG, nine of which form three groups of three to vote inputs controlling the three trip solenoids. A second TREG board may be driven from VPRO through J4.

## Installation

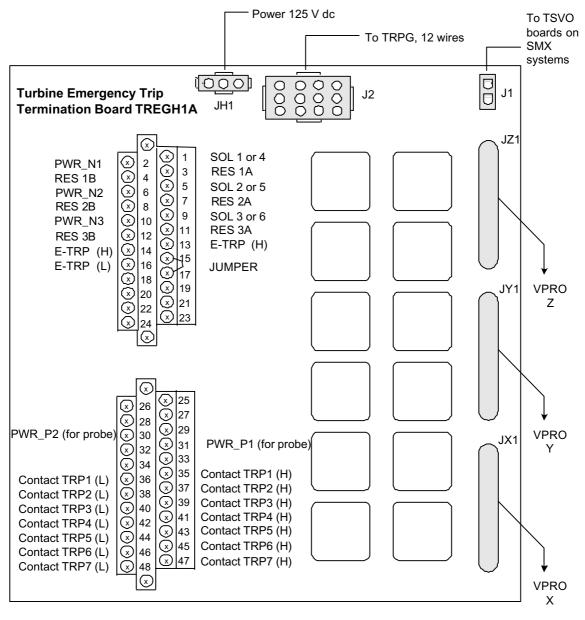

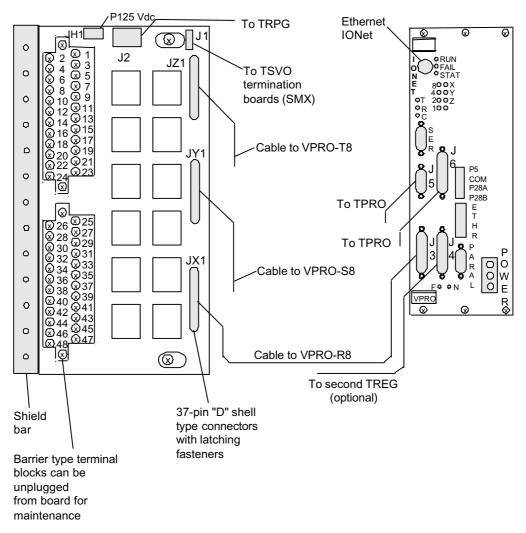

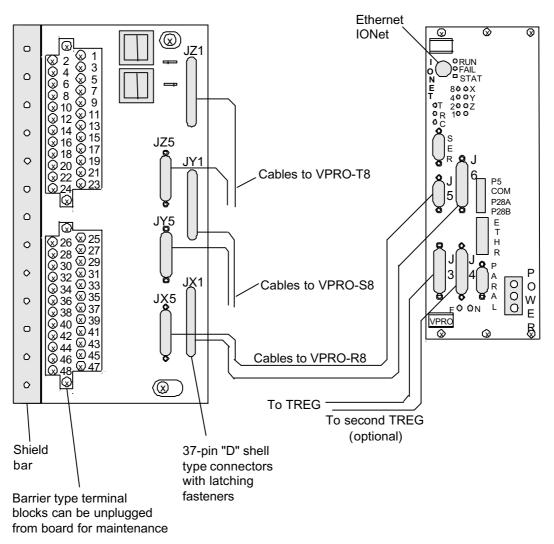

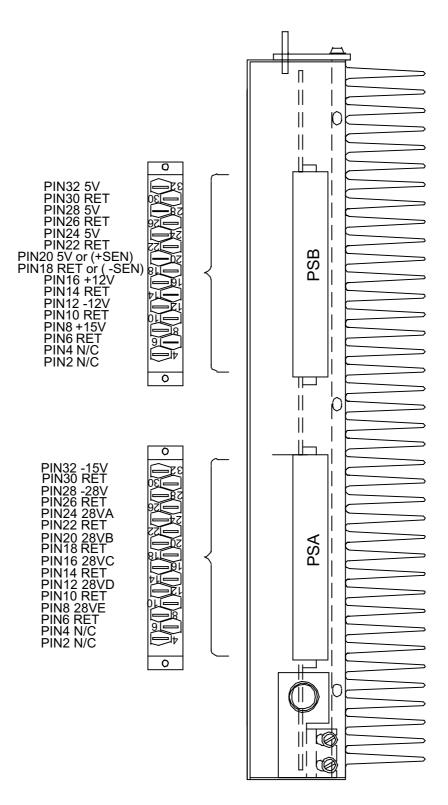

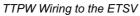

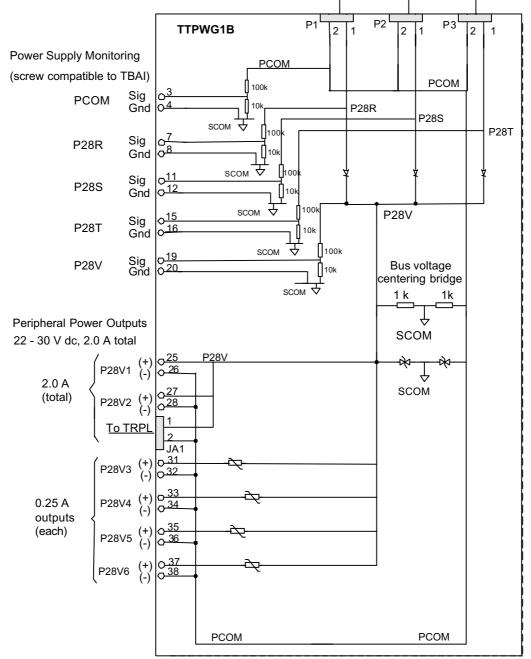

The three trip solenoids, economizing resistors, and the emergency stop are wired directly to the first I/O terminal block. Up to seven trip interlocks can be wired to the second terminal block. The wiring connections are shown in the following figure.

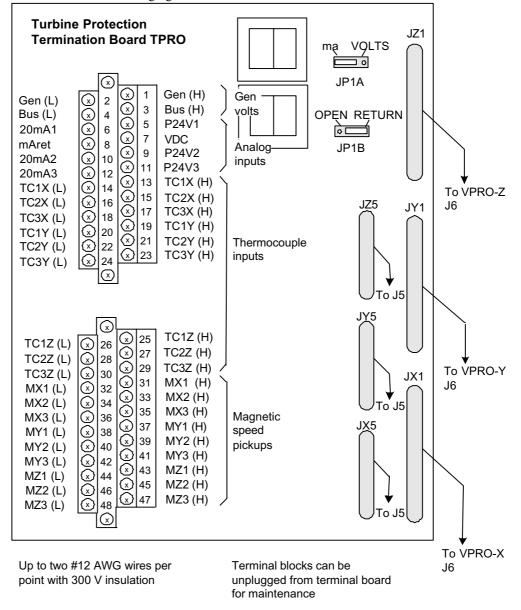

Up to two #12 AWG wires per point with 300 volt insulation

Terminal blocks can be unplugged from terminal board for maintenance

TREG Terminal Board

**TREG Terminal Board**

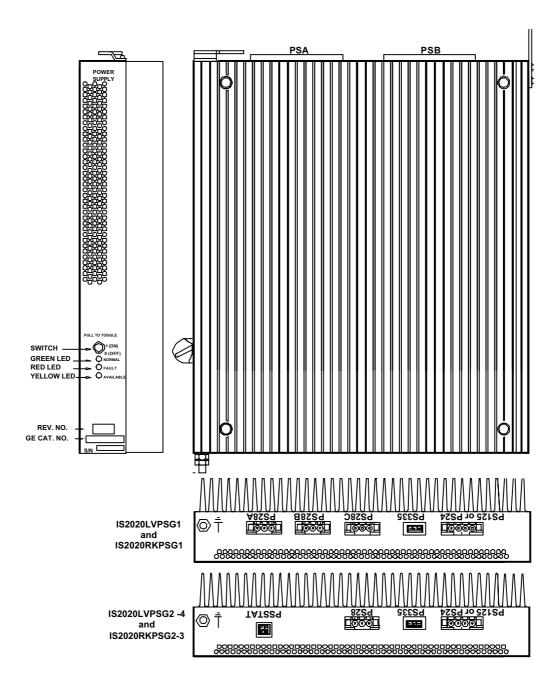

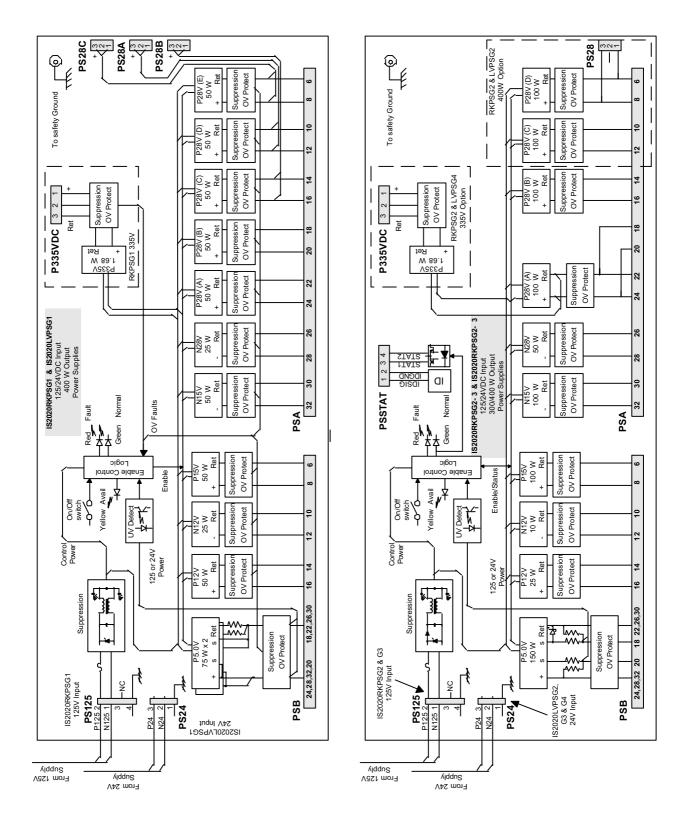

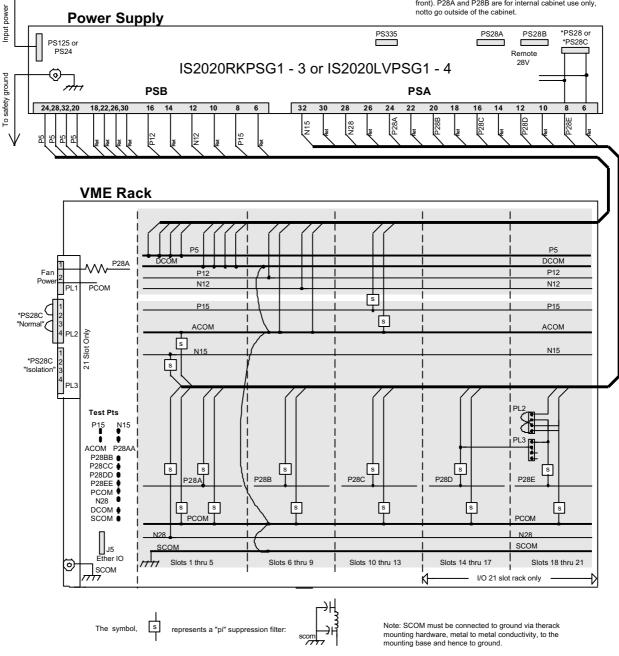

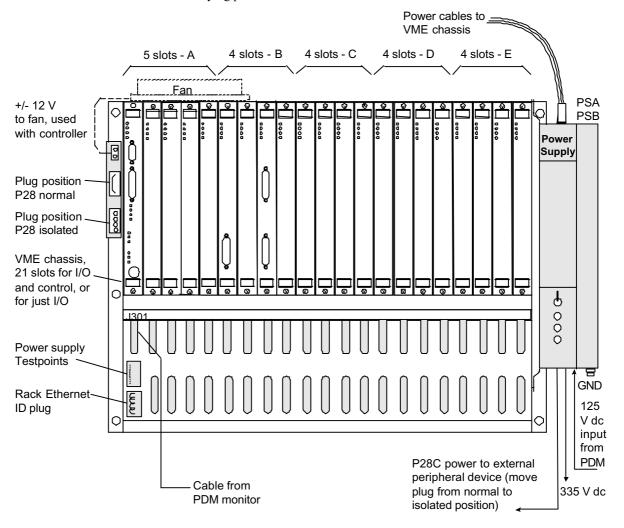

VPRO Module – R8

Trip Emergency Terminal Board, VPRO Board, and Cabling

TREG Board, Trip Interlocks, and Trip Solenoids

## Operation

The solenoid circuit has a metal oxide varistor (MOV) for current suppression and a 10 ohm, 70 watt economizing resistor.

. A normally closed contact from each relay is used to sense the relay status for diagnostics TREG is entirely controlled by VPRO, and the only connections to the control modules are the J2 power cable and the trip solenoids. In Simplex systems a third cable carries a trip signal from J1 to the TSVO terminal board, providing a servo valve clamp function upon turbine trip.

## **Control of Trip Solenoids**

Both TRPG and TREG control the trip solenoids so that either one can remove power and actuate the hydraulics to close the steam or fuel valves. The nine trip relay coils on TREG are supplied with 28 V dc from VPRO boards in X, Y, and Z. The trip solenoids are supplied with 125 V dc via plug J2, and draw up to 1 amp with a 0.1 second L/R time constant.

A separately fused 125 V dc feeder is provided from the turbine control for the solenoids which energize in the run mode and de-energize in the trip mode. Diagnostics monitor each 125 V dc feeder from the power distribution module at its point of entry on the terminal board to verify the fuse integrity and the cable connection.

Two series contacts from each emergency trip relay (ETR1, 2, 3) are connected to the positive 125 V dc feeder for each solenoid, and two series contacts from each primary trip relay (PTR1,2,3 in TRPG) are connected to the negative 125 V dc feeder for each solenoid. An economizing relay (KE1, 2, 3) is supplied for each solenoid with a normally closed contact in parallel with the current limiting resistor. These relays are used to reduce the current load after the solenoids are energized. The ETR and KE relay coils are powered from a 28 V dc source from the VPRO boards. Each VPRO board in each of the X, Y, and Z sections supplies an independent 28 V dc source.

The 28 V dc bus is current limited and used for power to an external manual emergency trip contact, shown as E-STOP. Three master trip relays (K4X, K4Y, K4Z) disconnect the 28 V dc bus from the ETR, and KE relay coils if a manual emergency trip occurs. Any trip which originates in either the protection module (such as EOS) or the TREG (such as a manual trip) will cause each of the three protection module sections to transmit a trip command over the IONet to the control module, and may be used to identify the source of the trip.

In addition, the K4CL servo clamp relay will energize and send a contact feedback directly from the TREG terminal board to the TSVO servo terminal board. TSVO disconnects the servo current source from the terminal block and applies a bias to drive the control valve closed. This is only used on Simplex applications to protect against the servo amplifier failing high. Note that the primary and emergency overspeed systems will trip the hydraulic trip solenoids independent of this circuit.

### Solenoid Trip Tests

Application software in the control module is used to initiate tests of the trip solenoids. Online tests allow each of the trip solenoids to be manually tripped one at a time either through the PTR relays from the control module(s) or through the ETR relays from the protection module. A contact from each solenoid circuit is wired back as a contact input to give a positive indication that the solenoid has tripped. Primary and emergency offline overspeed tests are provided too for verification of actual trips due to software simulated trip overspeed conditions.

## Specifications

| Item                                | Specification                                                                                                                       |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Number of trip solenoids (TREG)     | Three solenoids per TREG (total of 6 per VPRO)                                                                                      |

| Trip solenoid rating                | 125 V dc standard with 1 A draw<br>24 V dc is alternate with 1 A draw                                                               |

| Trip solenoid circuits              | Circuits rated for NEMA class E creepage and clearance<br>Circuits can clear a 15 A fuse with all circuits fully loaded             |

| Solenoid response time              | Solenoid L/R time constant is 0.1 second                                                                                            |

| Suppression                         | MOV across the solenoid                                                                                                             |

| Relay outputs                       | Three economizer relay outputs, two second delay to energize                                                                        |

|                                     | Driver to breaker relay K25A on TTUR                                                                                                |

|                                     | Servo clamp relay on TSVO                                                                                                           |

| Solenoid control relay contacts     | Contacts are rated to interrupt inductive solenoid loads at 125 V<br>dc, 1 A<br>Bus voltage can vary from 70 to 145 V dc            |

| Trip inputs                         | Seven trip interlocks to VPRO protection module, 125/24 V dc<br>One emergency stop hardwired trip interlock, 24 V dc                |

| Trip interlock excitation           | H1 - Nominal 125 V dc, floating, ranging from 100 to 145 V dc<br>H2 – Nominal 24 V dc, floating, ranging from 18.5 to 32 V dc       |

| Trip interlock current              | H1 for 125 V dc applications:<br>Circuits draw 2.5 mA (50 kohms)<br>H2 for 24 V dc applications:<br>Circuits draw 2.5 mA (10 kohms) |

| Trip interlock isolation            | Optical isolation to 1500 volts on all inputs                                                                                       |

| Trip interlock filter               | Hardware filter, 4 ms                                                                                                               |

| Trip interlock Ac voltage rejection | 60 V rms @ 50/60 Hz at 125 V dc excitation                                                                                          |

TREG Board Specifications

## Diagnostics

Descriptions of the TREG diagnostics are contained in the VPRO section. The diagnostics cover the trip relay driver and contact feedbacks, solenoid voltage, economizer relay driver and contact feedbacks, K25A relay driver and coil, servo clamp relay driver and contact feedback, and the solenoid voltage source.

Connectors JX1, JY1, and JZ1 on the terminal board have their own ID device that is interrogated by the I/O board. The ID device is a read-only chip coded with the terminal board serial number, board type, revision number, and the plug location.

## Configuration

TREG is configured using the toolbox. This software usually runs on a data-highway connected CIMPLICITY station or workstation. The following table summarizes the configuration choices and defaults. For details refer to GEH-6403 *Control System Toolbox for Configuring the Mark VI Turbine Controller*.

| Parameter       | Description                                                                              | Choices                  |

|-----------------|------------------------------------------------------------------------------------------|--------------------------|

| Configuration   |                                                                                          |                          |

| J3:IS200TREGH1A | First TREG Board                                                                         | Connected, not connected |

| KESTOP1_Fdbk1   | Emergency stop - When TREG, ESTOP1, inverse sense,<br>K4 relay, True = Run - board point | Point edit (input BIT)   |

| Contact1        | Trip interlock 1 (first of 7) - board point                                              | Point edit (input BIT)   |

| ContactInput    | Trip interlock 1 used                                                                    | Used, unused             |

| TripEnable      | Trip interlock active                                                                    | Enable, disable          |

| TrpTimeDelay    | Time delay before tripping turbine after contact opens (seconds)                         | 0 to 10                  |

| SeqOfEvents     | Record contact transitions in sequence of events                                         | Enable, disable          |

| K1_Fdbk         | Trip Relay 1 feedback (first of 3) - board point                                         | Point edit (input BIT)   |

| RelayOutput     | Relay feedback used                                                                      | Used, unused             |

| KE1_Fdbk        | Economizer relay for trip solenoid feedback (first of 3)<br>- board point                | Point edit (input BIT)   |

| RelayOutput     | Economizer relay feedback used                                                           | Used, unused             |

| K4CL_Fdbk       | Drive Control Valve Servos Closed, use ONLY for Steam<br>Turbine Simplex - board point   | Point Edit (Input BIT)   |

| Relay output    | Servo valve clamp used                                                                   | Used, unused             |

| K25A            | Synchronizing check relay on TTUR - board point                                          | Point edit (input BIT)   |

| SynchCheck      | Synch check relay K25A used                                                              | Used, unused             |

Typical TREG Configuration

| SystemFreq             | System frequency in Hz                                                               | 50 or 60                    |

|------------------------|--------------------------------------------------------------------------------------|-----------------------------|

| ReferFreq              | Select generator frequency reference for PLL, standard PR input or from signal space | PR standard or signal space |

| TurbRPM                | Rated load turbine RPM                                                               | 0 to 20,000                 |

| VoltageDiff            | Maximum voltage difference in kV rms for synchronizing                               | 0 to1,000                   |

| FreqDiff               | Maximum frequency difference in Hz for synchronizing                                 | 0 to 0.5                    |

| PhaseDiff              | Maximum phase difference in degrees for synchronizing                                | 0 to 30                     |

| GenVoltage             | Minimum generator voltage in kV rms for synchronizing                                | 1 to 1,000                  |

| BusVoltage             | Minimum bus voltage in kV rms for synchronizing                                      | 1 to 1,000                  |

| J4A:IS200TREGH1A       | Second TREG board                                                                    | Connected, not connected    |

| KESTOP2_Fdbk           | When TREG, ESTOP, inverse sense, K4 relay, True =<br>Run - board point               | Point edit (input BIT)      |

| K4_Fdbk                | Trip relay 4 feedback (first of three) - board point                                 | Point edit (input BIT)      |

| KE4_Fdbk               | Economizing relay for trip solenoid 4 (first of three) - board point                 | Point edit (input BIT)      |

| Board Points (Signals) | Description - Point Edit (Enter Signal Connnection)                                  | Direction Type              |

|                        | See point edit names above                                                           |                             |

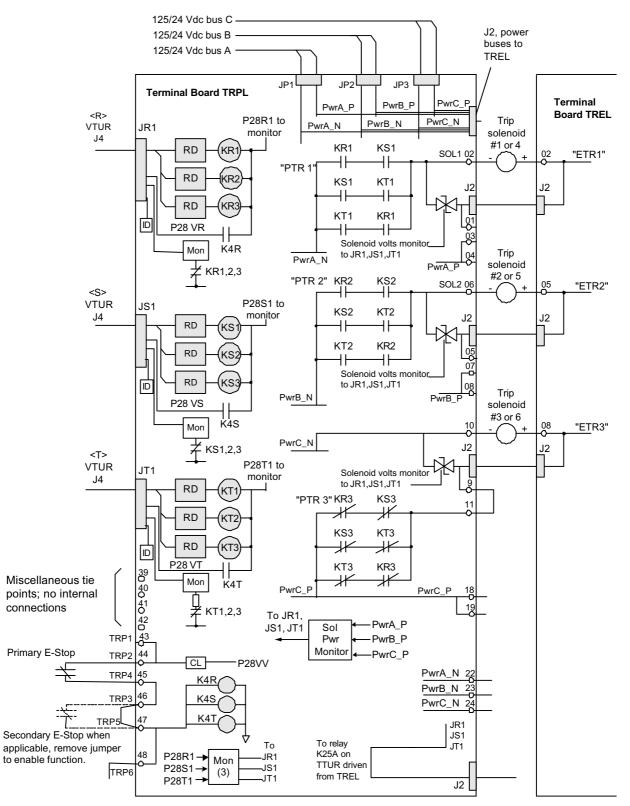

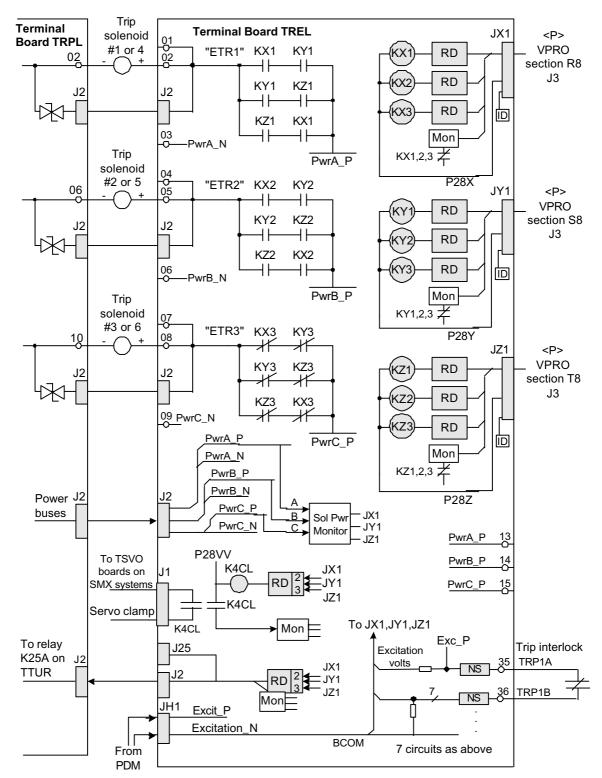

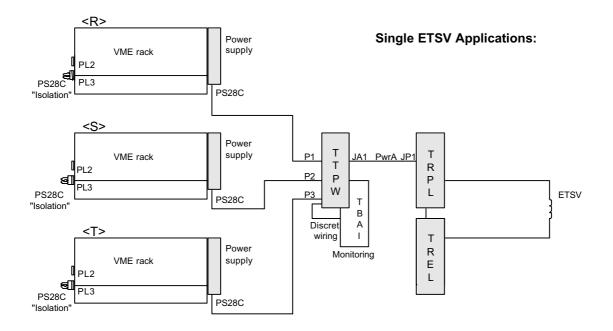

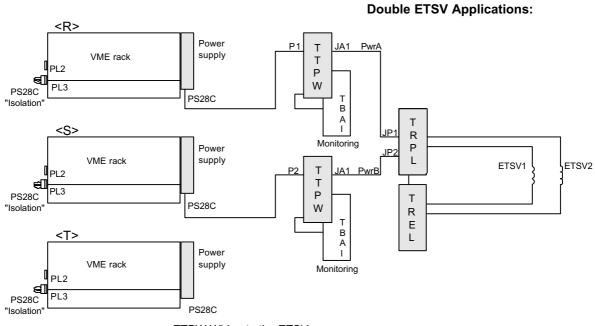

## TRPL/TREL Large Steam Turbine Primary and Emergency Trip

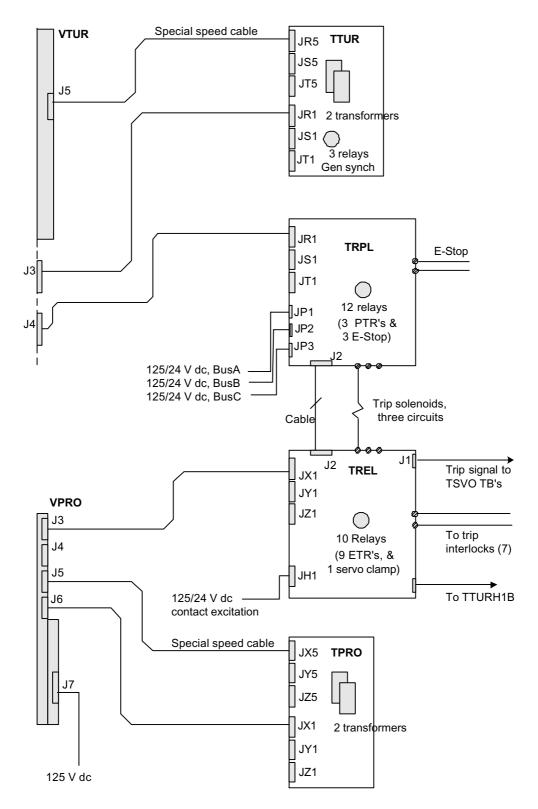

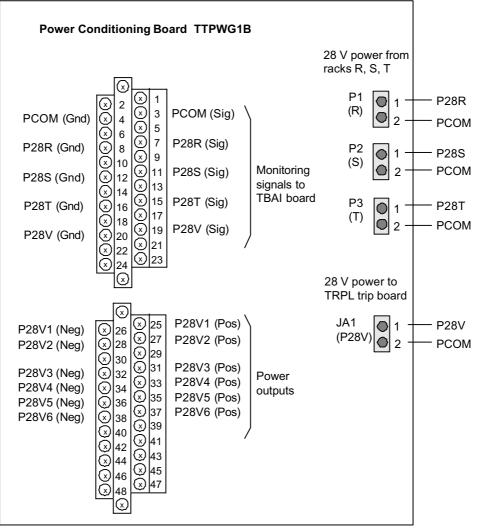

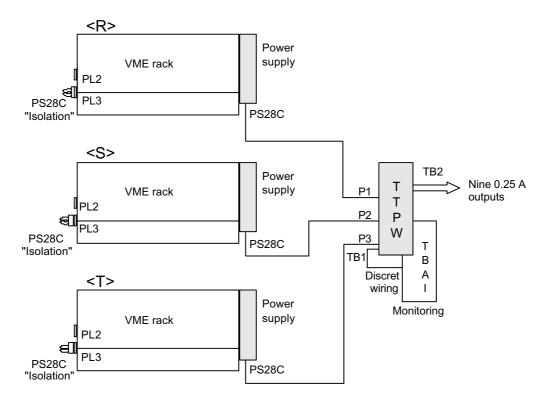

TRPL and TREL are used to provide primary and emergency overspeed protection for large steam turbines. These two terminal boards are used in a similar way as TRPG and TREG are used on gas turbine applications.

Up to three trip solenoids can be connected between the TREL and TRPL terminal boards. TREL provides the positive side of the 125 V dc to the solenoids and TRPL provides the negative side. VTUR provides primary overspeed protection and the emergency stop functions. It controls the 12 relays on TRPL, nine of which form three groups of three to vote inputs controlling the three trip solenoids.

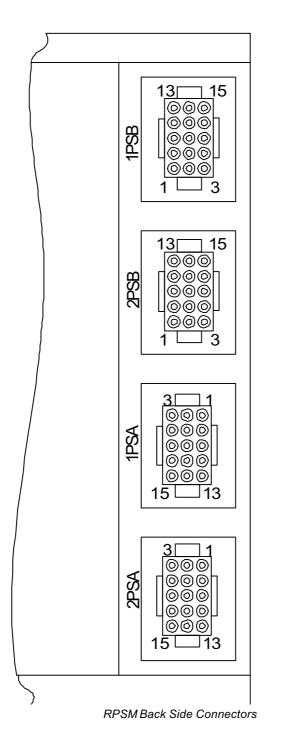

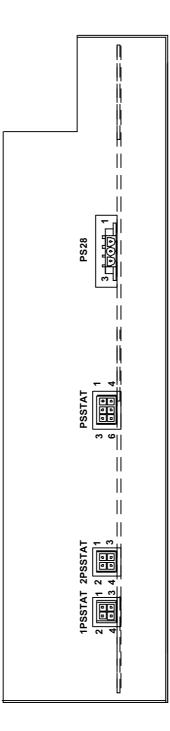

Steam Turbine Control and Protection Boards

### Features

TRPL is used for TMR applications only. Three separate power buses, PwrA, PwrB, PwrC for solenoid power, are brought in through connectors JP1, JP2, and JP3, and then distributed to TREL through connector J2. In the TREL, three separate power buses, PwrA, PwrB, PwrC for solenoid power, are brought in through connector J2 from TRPL.

The power buses have a nominal voltage of 125 V dc (70 to 145 V dc) or 24 V dc (18 to 32 V dc). The board includes power bus monitoring (three buses). The maximum current per bus is 3 amps.

Each of the three trip solenoids is controlled by three relays using 2/3 contact voting. The relay output rating (for 100,000 operations) is as follows:

- At 24 V dc, 3 A, L/R = 100 milliseconds, with suppression

- At 125 V dc, 1.0 A, L/R = 100 milliseconds, with suppression

The trip circuits include solenoid suppression, and associated solenoid voltage monitoring and trip relay contact monitoring. In the TRPL, the hardwired trip (E-STOP) and associated monitoring provides approximately 6.6 V dc to VTUR when the K4 relays are picked up. In the TREL, seven dry contact inputs are used as trip interlocks, and the excitation and signal are monitored and fanned to the three VPROs.

## Configuration

TRPL configuration is similar to TRPG but there are no flame detectors. Only the single-wide VTUR is used with a single J4 connector.

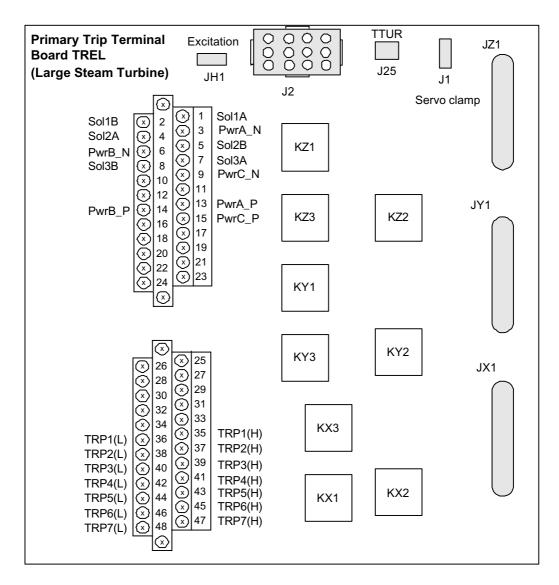

TREL configuration is similar to TREG but there are no emergency stop inputs (KESTOP), and no economizer relay solenoid feedbacks (KE#\_Fdbk). Only one TREL can be connected to the VPRO.

The TREL includes the synch check relay driver, K25A, and associated monitoring, the same as on TREG, and the servo clamp relay driver, K4CL, and its associated monitoring.

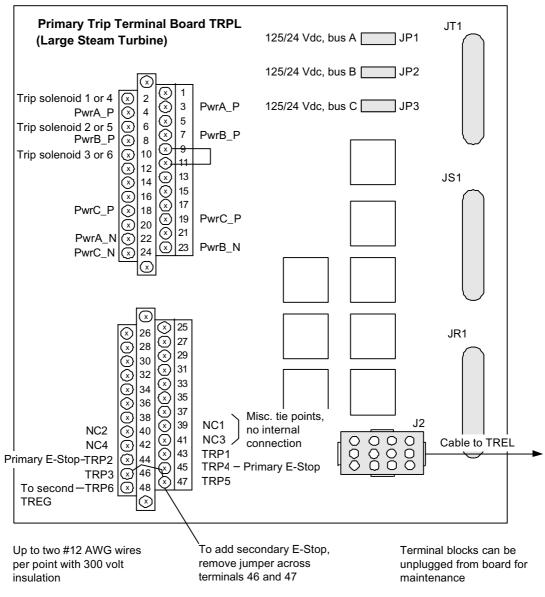

TRPL Terminal Board

TRPL Terminal Board (continued)

### Installation

The three trip solenoids are wired directly to the first I/O terminal block. The primary emergency stop and optional secondary emergency stop are wired to the second terminal block. Trip solenoid power is supplied through plugs JP1, JP2, and JP3. The wiring connections are shown in the following figures.

TRPL Terminal Board Wiring

Up to two #12 AWG wires per point with 300 V insulation

Terminal blocks can be unplugged from terminal board for maintenance

TREL Terminal Board Wiring

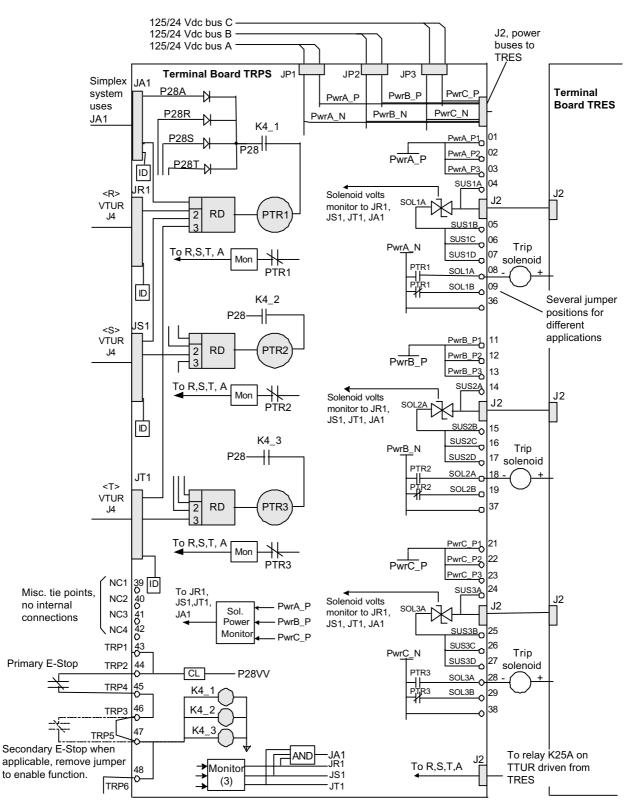

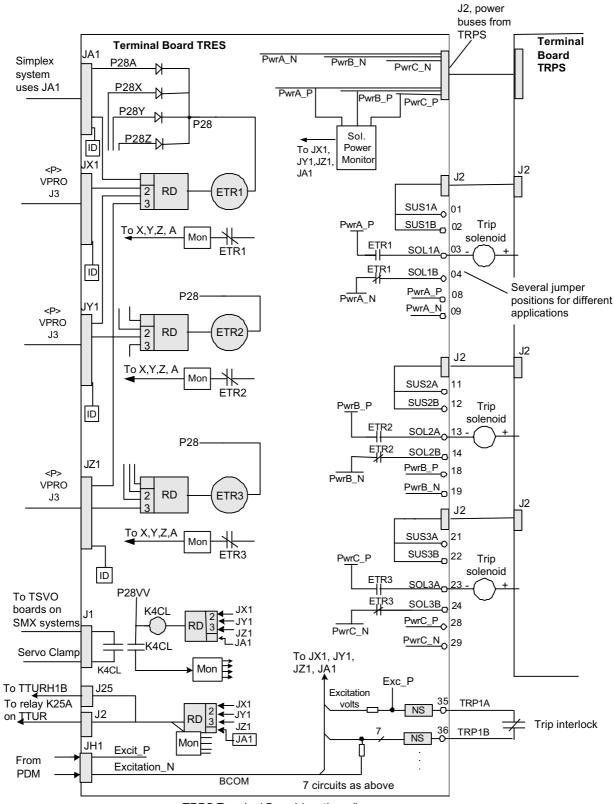

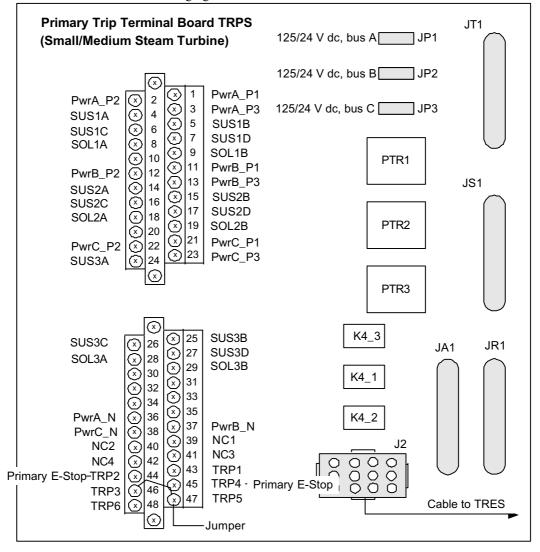

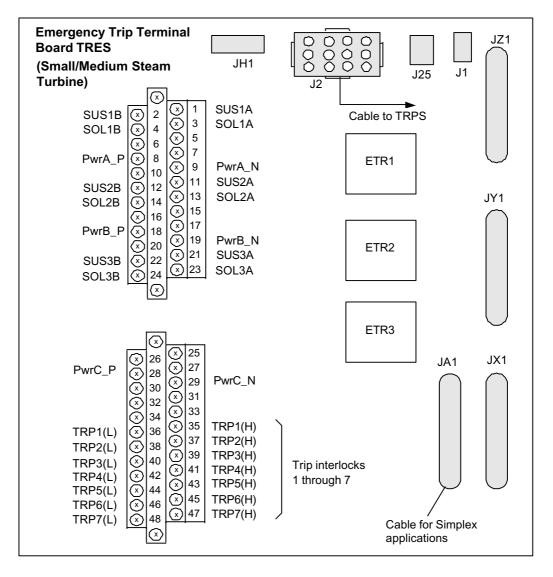

## TRPS/TRES Small/Medium Steam Turbine Primary Trip

TRPS and TRES are used to provide primary and emergency overspeed protection for small/medium size steam turbines. These two terminal boards are used in a similar way as TRPG and TREG are used on gas turbine applications.

Up to three trip solenoids can be connected between the TRES and TRPS terminal boards. TRES provides the positive side of the 125 V dc to the solenoids and TRPS provides the negative side.

VTUR provides primary overspeed protection and the emergency stop functions. It controls the six relays on TRPS, three of which control the three trip solenoids.

VPRO provides emergency overspeed protection and the trip functions. It controls the three relays on TRES, which control the three trip solenoids.

### Features

TRPS and TRES are used for both simplex and TMR applications. Three separate power buses, PwrA, PwrB, PwrC for solenoid power, are brought in the TRPS through connectors JP1, JP2, and JP3, and then distributed to TRES through connector J2.

The power buses have a nominal voltage of 125 V dc (70 to 145 V dc) or 24 V dc (18 to 32 V dc). The board includes power bus monitoring (three buses). The maximum current per bus is 3 amps.

Each of the three trip solenoids is controlled by a relay driver providing 2/3 logic voting with signals from JR1, JS1, and JT1. In the Simplex application, the relay driver is controlled by a single signal from JA1. The relay output rating (for 100,000 operations) is as follows:

- At 24 V dc, 3 A, L/R = 100 milliseconds, with suppression

- At 125 V dc, 1.0 A, L/R = 100 milliseconds, with suppression

The trip circuits include solenoid suppression, and associated solenoid voltage monitoring and trip relay contact monitoring. In the TRPS, the hardwired trip (E-STOP) and associated monitoring provides approximately 6.6 V dc to VTUR when the K4 relays are picked up.

In the TRES, seven dry contact inputs are used as trip interlocks, and the excitation and signal are monitored and fanned to the three VPROs. The board includes the synch check relay driver, K25A, and associated monitoring, the same as on TREG, and the servo clamp relay driver, K4CL, and its associated monitoring.

## Configuration

TRPS configuration has no flame detectors. Only the single-wide VTUR is used with a single J4 connector.

TRES configuration has no emergency stop, and no economizing relay feedback. Only one VPRO J3 connector is used; there can be no second TRES board.

TRPS Terminal Board

TRPS Terminal Board (continued)

### Installation

In the TRPS board, three trip solenoids are wired directly to the first and second I/O terminal blocks. The primary emergency stop and optional secondary emergency stop are wired to the second terminal block. Trip solenoid power is supplied throu0gh plugs JP1, JP2, and JP3. The wiring connections are shown in the following figure.

Up to two #12 AWG wires per point with 300 V insulation

Terminal blocks can be unplugged from terminal board for maintenance

TRPS Terminal Board Wiring

In the TRES board, the three trip solenoids are wired directly to the first I/O terminal block. The seven trip interlocks are wired to the second terminal block. Trip solenoid power is supplied through plug J2 from TRPS, and contact excitation comes through JH1 from the PDM. The wiring connections are shown in the following figure.

Up to two #12 AWG wires per point with 300 V insulation

Terminal blocks can be unplugged from terminal board for maintenance

TRES Terminal Board Wiring

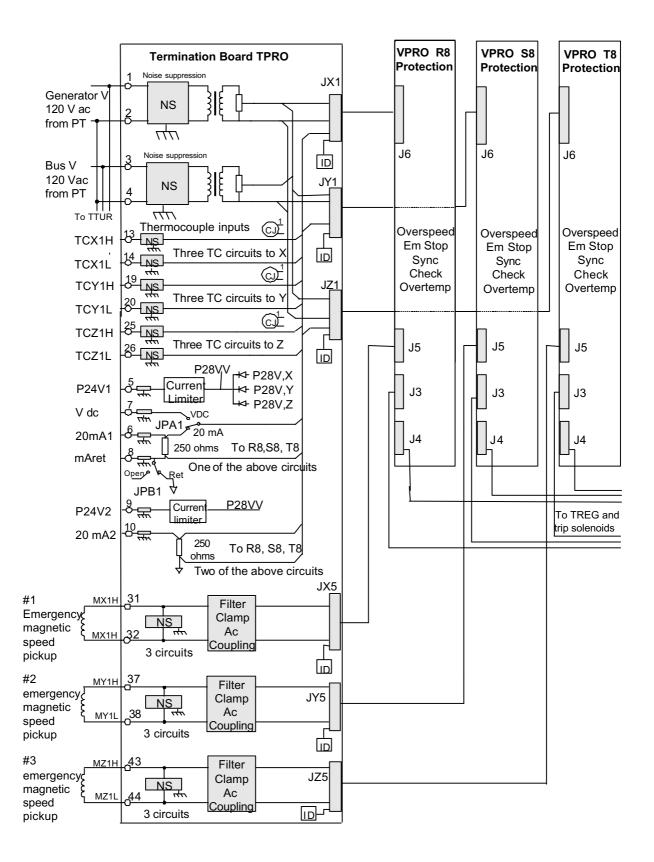

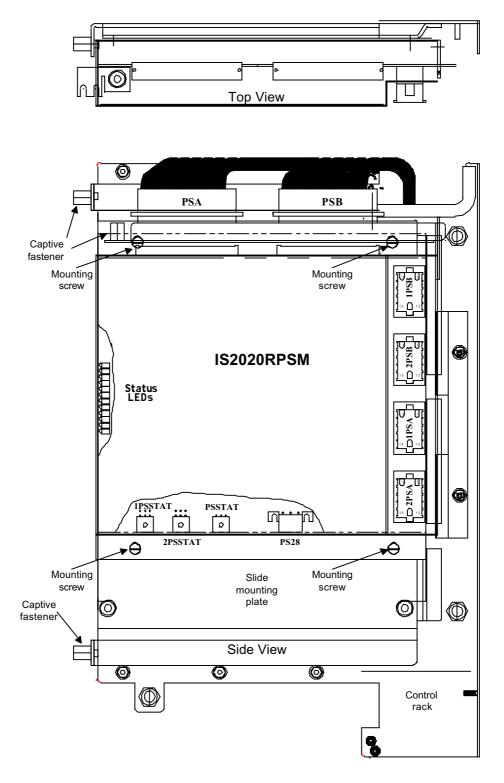

## **TPRO Turbine Protection Terminal Board**

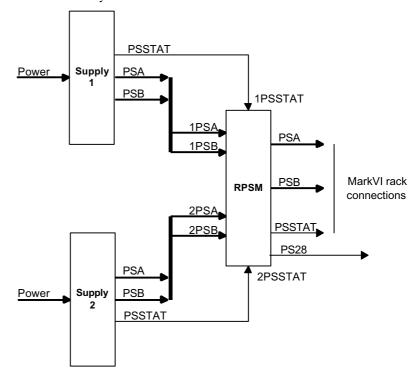

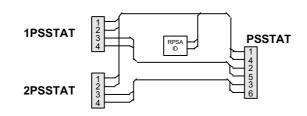

The VPRO) and associated terminal board (TPRO) provide an independent emergency overspeed protection system. The protection system consists of triple redundant VPRO boards in a module separate from the turbine control system, controlling the trip solenoids through TREG.

#### **TPRO Terminal Board**

**VPRO-R8**

Turbine Protection Terminal Board, VPRO Board, and Cabling

The following figure shows how the VTUR and VPRO processor boards share in the turbine protection scheme. Either one can independently trip the turbine through the relays on TRPG or TREG.

Turbine Control and Protection Boards

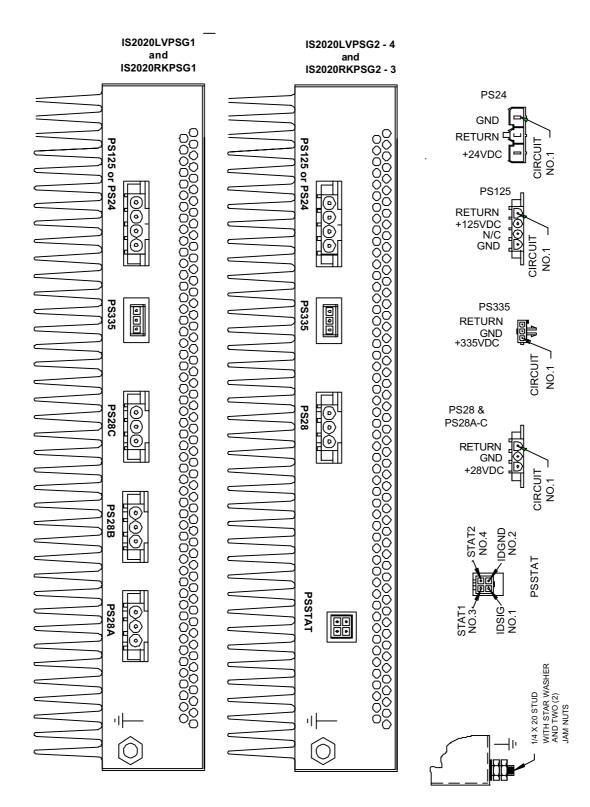

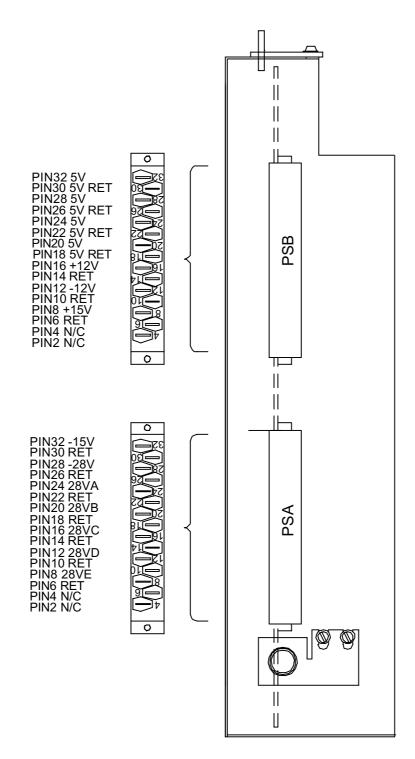

### Installation

The generator and bus potential transformers and the analog inputs are wired to the first TPRO terminal block. The magnetic speed pickups are wired to the second block. Jumpers JP1A and JP1B are set to give either a 4–20 mA or voltage input on the first of the three analog inputs. The wiring connections are shown in the following figure.

Terminal Board TPRO

## Operation

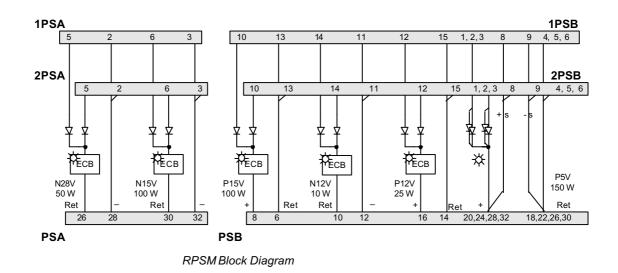

The main purpose of the <P> protection module is emergency overspeed (EOS) protection for the turbine. In addition, the module has backup synchronization check protection, three analog current inputs, and nine thermocouple inputs, primarily intended for exhaust overtemperature protection on gas turbines.

The protection module is always triple redundant with three completely separate and independent sections named X, Y, and Z. Any one of these sections can be powered down and replaced while the turbine is running without jeopardizing the protection system. Each section contains its own I/O interface, processor, power supply, and Ethernet communications (IONet) to the control modules. The communications allow initiation of test commands from the control module to the protection module and the monitoring of EOS system diagnostics in the control module and on the operator interface. Communications are resident on the VPRO board which is the heart of the system.

## Features

### Speed Control and Overspeed Protection

Speed control and overspeed protection is implemented with six passive, magnetic speed pickups. The first three are monitored by the control module(s) which use the median signal for speed control and the primary overspeed protection. The second three are separately connected to the X, Y, and Z sections of the protection module. Provision is made for nine passive magnetic speed pickups or active pulse rate transducers (TTL type) on the TPRO terminal board with three being monitored by each of the X, Y, and Z sections. Separate overspeed trip settings are programmed into the application software for the primary and emergency overspeed trip limits, and a second emergency overspeed trip limit must be programmed into the I/O configurator to confirm the EOS trip point.

The speed is calculated by counting passing teeth on the wheel and measuring the time involved. Another protection feature is the calculation of the rate of change of speed which is compared with 100%/sec and transmitted to the control module to trip the unit if it is detected after the turbine reaches a predetermined steady-state speed. This steady-state speed limit is a tuning constant located in the controller's application software. Another speed threshold which is monitored by the EOS system is 10% speed. This is transmitted to the control module to verify that there is no gross disagreement between the first set of three speed pickups being monitored by the controller (for speed control and the primary overspeed protection) and the second set of three speed pickups being monitored by the EOS system.

### Interface To Trip Solenoids

The trip system combines the primary trip interface from the control module(s) with the EOS trip interface from the protection module. Three separate, triple redundant trip solenoids (also called electrical trip devices - ETDs) are used to interface with the hydraulics. The ETDs are connected between the TRPG and TREG terminal boards. A separately fused 125 V dc feeder is provided from the turbine control for each solenoid which energize in the run mode and de-energize in the trip mode.

The VPRO board has a VME interface to allow programming and testing in a VME rack; however, the backplane is neutralized when plugged into the protection module to eliminate any continuity between the three independent sections.

### Backup Synch Check Protection

Backup synch check protection is provided in the  $\langle P \rangle$  protection module. The generator and bus voltages are supplied from two, single phase, potential transformers (PTs) secondary output supplying a nominal 115 V rms. The maximum cable length between the PTs and the turbine control is 100 meters of 18 AWG twisted, shielded wire. Each PT is magnetically isolated with a 1,500 V rms rated barrier and a circuit load less than 3 VA. The synch algorithms are based on phase lock loop techniques. Phase error between the generator and bus voltages is less than +/-1 degree at nominal voltage and 50/60 Hz. A frequency range of 45 to 66 Hz is supported with the measured frequency within 0.05% of the input frequency. The algorithm is illustrated under TTUR, generator synchronizing.

Each PT input is internally connected in parallel to the X, Y, and Z sections of the Protection Module. The triple redundant phase slip windows result in a voted logical output on the TREG terminal board which drives the K25A relay. This relay's contacts are connected in series with the synch permissive relay (K25P) and the auto synch relay (K25) to insure that no false command is issued to close the generator breaker. Similarly, contacts from the K25A contact are connected in series with the contacts from remote, manual synchronizing equipment to insure no false commands.

### Thermocouple and Analog Inputs

Thermocouple and analog inputs are available in the protection module, primarily for gas turbine applications. Nine thermocouple inputs are monitored with three connected to each section of the protection module. These are generally used for backup exhaust overtemperature protection. Also, one  $\pm$  5, 10 V dc, 4–20 mA (selectable) input, and two 4–20 mA inputs can be connected to the TPRO terminal board which feeds the inputs in parallel to the three sections of the protection module.

### **Power Supply**

Each VPRO board has its own on-board power supply. This generates 5 V dc and 28 V dc using 125 V dc supplied from the cabinet PDM. The entire TMR VPRO module therefore has three power supplies for high reliability.

### Specifications

VPRO Board Specifications

| Item             | Specificati | ion                                                                                                                                                                                                                 |

|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of inputs | TPRO:9      | Passive speed pickups<br>1 Generator and 1 bus voltage<br>9 Thermocouples<br>1 4–20 mA current or voltage<br>2 4–20 mA current                                                                                      |

|                  | VPRO: 3     | <ul> <li>Passive speed pickups</li> <li>Generator and 1 bus voltage</li> <li>Thermocouples</li> <li>4–20 mA current or voltage</li> <li>4–20 mA current</li> <li>Trip interlocks</li> <li>Emergency stop</li> </ul> |

| Number of Outputs                    | TREG:3                                                       | <ul> <li>Trip solenoids per TREG</li> <li>3 Economizer relays</li> <li>1 Breaker relay command, K25A on TTUR</li> <li>1 Servo clamp relay contact, to TSVO boards</li> </ul>                                                                                                      |

|--------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | VPRO:6                                                       | Trip solenoids<br>6 Economizer relays<br>1 Breaker relay command, K25A on TTUR<br>1 Servo clamp relay contact, to TSVO boards                                                                                                                                                     |

| Power Supply Voltage                 | TPRO: 28 V (                                                 | dc from X, Y, and Z boards, voted                                                                                                                                                                                                                                                 |

|                                      | VPRO: Input                                                  | supply 125 V dc (70–145 V dc)<br>Output 5 V dc and 28 V dc                                                                                                                                                                                                                        |

| Frame Rate                           | Up to 100 Hz                                                 | Ζ                                                                                                                                                                                                                                                                                 |

| MPU Characteristics                  | Output gene<br>block, with in<br>The maximu<br>The system a  | tance 200 ohms with inductance of 85 mH.<br>rates 150 V p-p into 60k ohms at the TPRO terminal<br>isufficient energy for a spark.<br>m short circuit current is approximately 100 mA.<br>applies up to 400 ohm normal mode load to the input<br>uce the voltage at the terminals. |

| MPU Cable                            | that shielded                                                | be up to 300 m (984 ft) from the cabinet, assuming<br>I pair cable is used, with typical 70 nF single ended or<br>ntial capacitance, and 15 ohms resistance.                                                                                                                      |

| MPU Pulse Rate Range                 | 2 Hz to 20 kł                                                | Hz                                                                                                                                                                                                                                                                                |

| MPU Pulse Rate Accuracy              | Noise of the                                                 | ding; resolution is 15 bits at 100 Hz acceleration measurement is less than $\pm$ 50 Hz/sec Hz signal being read at 10 ms.                                                                                                                                                        |

| MPU Input Circuit Sensitivity        |                                                              | nal is 27 mV pk at 2 Hz<br>nal is 450 mV pk at 14 kHz                                                                                                                                                                                                                             |

| Generator and Bus Voltage<br>Sensors | Voltage accu<br>Frequency a<br>Phase differe<br>Allowable vo | hase potential transformers, 115 V rms secondary<br>uracy is 0.5% of rated V rms<br>ccuracy 0.05%<br>ence measurement better than 1 degree.<br>Itage range for synchronizing is 75 to 130 V rms.<br>as a load of less than 3 VA.                                                  |

| Thermocouple Inputs                  | Same specifi                                                 | ications as for VTCC board                                                                                                                                                                                                                                                        |

| Analog Inputs                        | Same specifi                                                 | cations as for VAIC board                                                                                                                                                                                                                                                         |

## Diagnostics

Board diagnostics cover the thermocouple limits, reference voltage, cold junction, analog input health, and contact input test failure. Relay diagnostics cover the trip relay driver and contact feedbacks, solenoid voltage, economizer relay driver and contact feedbacks, K25A relay driver and coil, and the servo clamp relay driver and contact feedback. Voltage diagnostics cover the solenoid power bus, and the voltage to the solenoids.

Connectors JX1, JY1, JZ1, JX5, JY5, and JZ5 on the terminal board have their own ID device, which is interrogated by the I/O board. The ID device is a read-only chip coded with the terminal board serial number, board type, revision number, and the plug location.

## Configuration

Typical VPRO-TPRO Configuration

| Parameter       | Description                                                                           | Choices                                                                                             |

|-----------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Configuration   |                                                                                       |                                                                                                     |

| Turbine_Type    | Define the type of turbine from selection of ten types                                | Two gas turbine<br>Two LM<br>Two large steam<br>One medium steam<br>One small steam<br>Two stage GT |

| LMTripZEnable   | On LM machine, when no PR on Z, enable vote for trip                                  | Enable, disable                                                                                     |

| OT_Trip_Enbl    | Enable overtemperature trip                                                           | Enable, disable                                                                                     |

| OvrTemp_Trip    | Iso-thermal overtemperature trip setting for exhaust thermocouples in degree F        | -60 to 2,000                                                                                        |

| CPD_Corner      | Overtemperature trip compressor discharge<br>pressure in psi at which CDP bias starts | 0 to 450                                                                                            |

| CPD_Slope       | Overtemperature trip compressor discharge pressure<br>bias slope in degrees F/psi     | -10 to 0                                                                                            |

| TA_Trip_Enab1   | Steam, enable trip anticipation on ETR1                                               | Enable, disable                                                                                     |

| RatedRPM_TA     | Steam, rated RPM, used for trip anticipation calculation                              | 0 to 20,000                                                                                         |

| Auto Reset      | Automatic restoring of thermocouples removed from scan                                | Enable, disable                                                                                     |

| DiagSolPwrA     | When using TREL/TRES, solenoid power, BusA, diagnostic enable                         | Enable, disable                                                                                     |

| Min_MA_Input    | Minimum mA for healthy 4–20 mA Input                                                  | 0 to 21                                                                                             |

| Max_MA_Input    | Maximum mA for healthy 4–20 mA Input                                                  | 0 to 21                                                                                             |

| AccelCalType    | Select acceleration calculation type                                                  | Slow, medium, fast                                                                                  |

| J5:IS200TPROH1A | J5 cable section of TPRO board                                                        |                                                                                                     |

| PulseRate1      | First of three speed inputs - board point                                             | Point edit (input FLOAT)                                                                            |

| PRType          | Selects gearing (resolution)                                                          | Unused, PR<6,000 Hz,<br>PR>6,000 Hz                                                                 |

| PRScale         | Pulses per revolution (output RPM)                                                    | 0 to 1,000                                                                                          |

| OS_Setpoint     | Overspeed trip setpoint in RPM                                                        | 0 to 20,000                                                                                         |

| OS_Tst_Delta    | Offline overspeed test setpoint delta in RPM                                          | -2,000 to 2,000                                                                                     |

| Zero_Speed      | Zero speed for this shaft in RPM                                                      | 0 to 20,000                                                                                         |

| Min_Speed       | Minimum speed for this shaft in RPM                                                   | 0 to 20,000                                                                                         |

| Accel_Trip      | Enable Acceleration trip                                                              | Enable, disable                                                                                     |

| Acc-Setpoint    | Accelerate trip setpoint in RPM/second                                                | 0 to 20,000                                                                                         |

| TMR_DiffLimt    | Difference limit for voted pulse rate inputs in engineering units                     | 0 to 20,000                                                                                         |

| J6:IS200TPROH1A | J6 cable section of TPRO board                                                        |                                                                                                     |

|                 |                                                                                       |                                                                                                     |

| BusPT_KVolts           | kV rms, bus potential transformer - board point                                | Point edit (input FLC              | DAT)       |

|------------------------|--------------------------------------------------------------------------------|------------------------------------|------------|

| PT_Input               | PT input in kV rms for PT_Output                                               | 0 to 1,000                         |            |

| PT_Output              | PT output in V rms for PT_Input-typically 115                                  | 60 to 150                          |            |

| TMR_DiffLimt           | Difference limit for voted PT inputs in %                                      | 0 to 100                           |            |

| GenPT_KVolts           | kV rms, generator PT, configuration similar to bus PT - board point            | Point edit (input FLC              | DAT)       |

| TC11                   | Thermocouple 1, for X module (first of 3) - board point                        | Point edit (input FLC              | DAT)       |

| ThermCpIType           | Select thermocouple type or mV input                                           | Unused, mV, T, K, J,               | E          |

| Low pass filter        | Enable 2 Hz low pass filter                                                    | Enable, disable                    |            |

| TC21                   | Thermocouple 1, for Y module (first of three) configure as above - board point | Point edit (input FLC              | DAT)       |

| TC31                   | Thermocouple 1, for Z module (first of three) configure as above - board point | Point edit (input FLC              | DAT)       |

| Cold Junction          | CJ for thermocouples 1-3                                                       | Point edit (input FLC              | DAT)       |

| TMR_DiffLimt           | Difference limit for voted TMR CJ inputs in degrees F                          | -60 to 2,000                       |            |

| AnalogIn1              | First of three analog inputs - board point                                     | Point edit (input FLC              | DAT)       |

| Input Type             | Type of analog input                                                           | Unused, 4–20 mA, $\pm$             | 10 V       |

| Low_Input              | Input mA at low value                                                          | -10 to 20                          |            |

| Low_Value              | Input value in engineering units at low value                                  | -3.402e+38 to 3.402                | e+38       |

| High_Input             | Input mA at high value                                                         | -10 to 20                          |            |

| High_Value             | Input value in engineering units at high mA                                    | -3.402e+38 to 3.402e+38            |            |

| InputFilter            | Filter bandwidth in Hz                                                         | Unused, 12 Hz, 6 Hz<br>Hz, 0.75 Hz | , 3Hz, 1.5 |

| Trip_Enable            | Enable trip for this mA Input                                                  | Enable, disable                    |            |

| TripSetpoint           | Trip setpoint in engineering units                                             | -3.402e+38 to 3.402                | e+38       |

| TripTimeDelay          | Time delay before tripping turbine after signal exceeds setpoint in seconds    | 0 to 10                            |            |

| TMR_DiffLimt           | Difference limit for voted TMR inputs in % of<br>(High_Value-Low_Value)        | 0 to 100                           |            |

| J3:IS200TREGH1A        | First TREG board (see TREG section for configuration)                          | Connected, not conn                | ected      |

| J4:IS200TREGH1A        | Second TREG board (optional)                                                   | Connected, not conn                | ected      |

| Board Points (Signals) | Description - Point Edit (Enter Signal Connection)                             | Direction                          | Туре       |

| L3DIAG-VPRO1           | Board diagnostic                                                               | Input                              | BIT        |

| L3DIAG-VPRO2           | Board diagnostic                                                               | Input                              | BIT        |

| L3DIAG-VPRO3           | Board diagnostic                                                               | Input                              | BIT        |

| PR1_Zero               | L14HP_ZE                                                                       | Input                              | BIT        |

| PR2_Zero               | L14IP_ZE                                                                       | Input                              | BIT        |

| PR3_Zero               | L14LP_ZE                                                                       | Input                              | BIT        |

| Spare                  | Spare                                                                          | Input                              | BIT        |

| OS1_Trip               | L12HP_TP                                                                       | Input                              | BIT        |

|                        |                                                                                |                                    |            |

| OS2_Trip     | L12IP_TP                                 | Input | BIT |

|--------------|------------------------------------------|-------|-----|

| OS3_Trip     | L12LP_TP                                 | Input | BIT |

| Dec1_Trip    | L12HP_DEC                                | Input | BIT |

| Dec2_Trip    | L12IP_DEC                                | Input | BIT |

| Dec3_Trip    | L12LP_DEC                                | Input | BIT |

| Acc1_Trip    | L12HP_ACC                                | Input | BIT |

| Acc2_Trip    | L12IP_ACC                                | Input | BIT |

| Acc3_Trip    | L12LP_ACC                                | Input | BIT |

| TA_Trip      | Trip anticipate trip L12TA_TP            | Input | BIT |

| TA_StpLoss   | L30TA                                    | Input | BIT |

| OT_Trip      | L26TRP                                   | Input | BIT |

| MA1_Trip     | L3MA_TRP1                                | Input | BIT |

| MA2_Trip     | L3MA_TRP2                                | Input | BIT |

| MA3_Trip     | L3MA_TRP3                                | Input | BIT |

| SOL1_Vfdbk   | When TREG, trip solenoid 1 voltage       | Input | BIT |

| :            | :                                        | Input | BIT |

| SOL6_Vfdbk   | When TREG, trip solenoid 6 voltage       | Input | BIT |

| L25A_Cmd     | L25A breaker close pulse                 | Input | BIT |

| Cont1_TrEnab | Configure - Contact 1 trip enabled       | Input | BIT |

| :            | :                                        | Input | BIT |

| Cont7_TrEnab | Configure - Contact 7 trip enabled       | Input | BIT |

| Acc1_TrEnab  | Configure - Accelerate 1 trip enabled    | Input | BIT |

| :            | :                                        | Input | BIT |

| Acc3_TrEnab  | Configure - Accelerate 3 trip enabled    | Input | BIT |

| OT-TrEnab    | Configure - Overtemperature trip enabled | Input | BIT |

| GT_1Shaft    | Configure - Gas turbine, 1 shaft enabled | Input | BIT |

| GT_2Shaft    | Configure - Gas turbine, 2 shaft enabled | Input | BIT |

| LM_2Shaft    | Configure - LM turbine, 2 shaft enabled  | Input | BIT |

| LM_3Shaft    | Configure - LM turbine, 3 shaft enabled  | Input | BIT |

| LargeSteam   | Configure - Large steam 1, enabled       | Input | BIT |

| MediumSteam  | Configure - Medium steam, enabled        | Input | BIT |

| SmallSteam   | Configure - Small steam, enabled         | Input | BIT |

| STag_GT_1S   | Configure - Stage 1 shaft, enabled       | Input | BIT |

| STag_GT_2S   | Configure - Stage 2 shaft, enabled       | Input | BIT |

| ETR1_Enab    | Configure - ETR1 relay enabled           | Input | BIT |

| :            | :                                        | Input | BIT |

| ETR6_Enab    | Configure - ETR6 relay enabled           | Input | BIT |

| K4CL_Enab    | Configure - Servo clamp relay enabled    | Input | BIT |

| K25A_Enab    | Configure - Sync check relay enabled     | Input | BIT |

|              | g                                        |       |     |

| LSCFG1_TripHP configure tripInputBITLSCFG2_TripIP configure tripInputBITLSCFG3_TripLP configure tripInputBITOS1_SP_CfgErIP overspeed setpoint configure mismatch errorInputBITOS2_SP_CfgErIP overspeed setpoint configure mismatch errorInputBITComposTrip1Composite trip 1InputBITComposTrip2Composite trip 3InputBITLSESTOP1ESTOP 1 trip, TREG, J3InputBITLSESTOP1ESTOP 2 trip, TREG, J4InputBITLSESTOP1ESTOP 2 trip, TREG, J4InputBITLSCont1_TripContact 7 tripInputBITLSCont7_TripContact 7 tripInputBITLSCont7_TripContact 7 tripInputBITBus FreqSFL 2 HzInputBITGenFreqSFL 2 HzInputFLOATGenFreq 0ffSFDIFF2 slip Hz - generator low is negativeInputFLOATGenFreqDiffSSDIFF2 slip Hz - generator lag is negativeInputFLOATPR1_AccelHP accelerate in RPM/secondInputFLOATPR2_AccelLP accelerate in RPM/secondInputFLOATPR3_AccelLP accelerate in RPM/secondInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                   |        |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------|--------|-------|

| L5CFG3_Trip       LP configure trip       Input       BIT         OS1_SP_CfgEr       HP overspeed setpoint configure mismatch error       Input       BIT         OS2_SP_CfgEr       LP overspeed setpoint configure mismatch error       Input       BIT         OS3_SP_CfgEr       LP overspeed setpoint configure mismatch error       Input       BIT         ComposTrip1       Composite trip 2       Input       BIT         ComposTrip2       Composite trip 2       Input       BIT         L5ESTOP1       ESTOP 2 trip, TREG, J3       Input       BIT         L5ESTOP2       ESTOP 2 trip, TREG, J4       Input       BIT         L5Cont1_Trip       Contact 7 trip       Input       BIT         L5Cont7_Trip       Contact 7 trip       Input       BIT         L9StaftLock       LP shaft locked       Input       BIT         Bus Freq       SF 2 Hz       Input       FLOAT         GenFreq0       SF 2 Hz       Input       FLOAT         GenVoltsDiff       DV_ERR kV rms - generator low is negative       Input       FLOAT         GenFreq0iff       SFDIFF2 shape degrees - generator lag is negative       Input       FLOAT         PR1_Accel       HP accelerate in RPM/second       Input       FLOAT     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | L5CFG1_Trip   | HP configure trip                                 | Input  | BIT   |

| OS1_SP_CfgErHP overspeed setpoint configure mismatch errorInputBITOS2_SP_CfgErIP overspeed setpoint configure mismatch errorInputBITOS3_SP_CfgErLP overspeed setpoint configure mismatch errorInputBITComposTrip1Composite trip 1InputBITComposTrip2Composite trip 2InputBITComposTrip3Composite trip 3InputBITL5ESTOP1ESTOP 1 trip, TREG, J3InputBITL5ESTOP2ESTOP 2 trip, TREG, J4InputBITL5Cont1_TripContact 1 tripInputBITL5Cont7_TripContact 7 tripInputBITL5Cont7_TripContact 7 tripInputBITL6Cont7_TripContact 7 tripInputBITGenFreqSF 2 HzInputFLOATGenFreqSF 2 HzInputFLOATGenPhaseDiffSFDIFF2 slip Hz - generator low is negativeInputFLOATPR1_AccelHP accelerate in RPM/secondInputFLOATPR3_AccelLP accelerate in RPM/secondInputFLOATPR3_AccelLP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATPR4_Max<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | L5CFG2_Trip   | IP configure trip                                 | Input  | BIT   |

| OS2_SP_CfgEr       IP overspeed setpoint configure mismatch error       Input       BIT         OS3_SP_CfgEr       LP overspeed setpoint configure mismatch error       Input       BIT         ComposTrip1       Composite trip 1       Input       BIT         ComposTrip2       Composite trip 2       Input       BIT         ComposTrip3       Composite trip 3       Input       BIT         LSESTOP1       ESTOP 1 trip. TREG, J3       Input       BIT         LSESTOP2       ESTOP 2 trip. TREG, J4       Input       BIT         LSCont1_Trip       Contact 1 trip       Input       BIT         LSCont7_Trip       Contact 7 trip       Input       BIT         LPShaftLock       LP shaftLocked       Input       BIT         Bus Freq       SFL 2 Hz       Input       FLOAT         GenFreq       SFL 2 Hz       Input       FLOAT         GenPhaseDiff       SDIFF2 slip Hz - generator low is negative       Input       FLOAT         PR1_Accel       IP accelerate in RPM/second       Input       FLOAT         PR2_Accel       IP accelerate in RPM/second       Input       FLOAT         PR3_Accel       LP accelerate in RPM/second       Input       FLOAT         PR3_Max       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | L5CFG3_Trip   | LP configure trip                                 | Input  | BIT   |

| OS3_SP_CfgErLP overspeed setpoint configure mismatch errorInputBITComposTrip1Composite trip 1InputBITComposTrip2Composite trip 2InputBITComposTrip3Composite trip 3InputBITL5ESTOP1ESTOP 2 trip, TREG, J3InputBITL5ESTOP2ESTOP 2 trip, TREG, J4InputBITL5Cont7_TripContact 1 tripInputBITL5Cont7_TripContact 7 tripInputBITL9ShaftLockLP shaft lockedInputBITBus FreqSF 2 HzInputFLOATGen VolsDiffDV_ERR kV rms - generator low is negativeInputFLOATGen VolsDiffSDIFF2 shase degrees - generator lag is negativeInputFLOATGenPreqDiffSSDIFF2 phase degrees - generator lag is negativeInputFLOATPR1_AccelHP accelerate in RPM/secondInputFLOATPR1_AccelLP accelerate in RPM/secondInputFLOATPR3_AccelLP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATSynCk_PermL25A_PERM - sync check permissiveOutputBITOnLineOS1XtL97HP_TST1 - online HP overspeed testOutputBITOnLineOS1XtL97HP_TST2 - online HP overspeed testOutputBITOnLineOS1XtL97HP_TST2 - online HP overspeed test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OS1_SP_CfgEr  | HP overspeed setpoint configure mismatch error    | Input  | BIT   |

| ComposTrip1         Composite trip 1         Input         BIT           ComposTrip2         Composite trip 2         Input         BIT           ComposTrip3         Composite trip 3         Input         BIT           L5ESTOP1         ESTOP 1 trip, TREG, J3         Input         BIT           L5ESTOP2         ESTOP 2 trip, TREG, J4         Input         BIT           L5Cont1_Trip         Contact 1 trip         Input         BIT           L5Cont7_Trip         Contact 7 trip         Input         BIT           L9StaftLock         LP shaft locked         Input         BIT           Bus Freq         SFL 2 Hz         Input         FLOAT           GenFreq Off         DV_ERR kV rms - generator low is negative         Input         FLOAT           GenPhaseDiff         SDIFF2 phase degrees - generator lag is negative         Input         FLOAT           PR1_Accel         HP accelerate in RPM/second         Input         FLOAT           PR3_Accel         LP accelerate in RPM/second         Input         FLOAT           PR3_Max         LP maximum speed since last zero speed in RPM         Input         FLOAT           PR3_Max         LP maximum speed since last zero speed in RPM         Input         FLOAT           P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OS2_SP_CfgEr  | IP overspeed setpoint configure mismatch error    | Input  | BIT   |

| ComposTrip2Composite trip 2InputBITComposTrip3Composite trip 3InputBITL5ESTOP1ESTOP 1 trip, TREG, J3InputBITL5ESTOP2ESTOP 2 trip, TREG, J4InputBITL5Cont1_TripContact 1 tripInputBITL5Cont1_TripContact 1 tripInputBITL5Cont1_TripContact 7 tripInputBITL5Cont7_TripContact 7 tripInputBITBus FreqSFL 2 HzInputFLOATGenFreqSF 2 HzInputFLOATGenFreqDiffSFDIFF2 slip Hz, generator low is negativeInputFLOATGenFreqDiffSFDIFF2 slip Hz, generator slow is negativeInputFLOATPR1_AccelHP accelerate in RPM/secondInputFLOATPR2_AccelIP accelerate in RPM/secondInputFLOATPR3_AccelLP accelerate in RPM/secondInputFLOATPR4_MaxHP maximum speed since last zero speed in RPMInputFLOATPR2_MaxL25A_PERM - sync check permissiveOutputBITSynCk_PermL25A_PERM - sync check papassOutputBITOnLineOS1TstL97H_TST1 - online HP overspeed testOutputBITOnLineOS1TstL97H_TST1 - online HP overspeed testOutputBITOffLineOS3TstL97L_TST2 - offline IP overspeed testOutputBITOffLineOS3TstL97L_TST2 - offline IP overspeed testOutputBITOffLineOS3TstL97L_TST2 - offline IP overspe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OS3_SP_CfgEr  | LP overspeed setpoint configure mismatch error    | Input  | BIT   |

| ComposTrip3Composite trip 3InputBITL5ESTOP1ESTOP 1 trip, TREG, J3InputBITL5ESTOP2ESTOP 2 trip, TREG, J4InputBITL5Cont1_TripContact 1 tripInputBIT:::InputBITESTOP 2 trip, TREG, J4InputBITL5Cont1_TripContact 1 tripInputBITL5Cont7_TripContact 7 tripInputBITL9ShaftLockLP shaft lockedInputBITBus FreqSFL 2 HzInputFLOATGenFreqSF 2 HzInputFLOATGenFreqDiffSFDIFF2 slip Hz - generator low is negativeInputFLOATGenPhaseDiffSSDIFF2 phase degrees - generator lag is negativeInputFLOATPR1_AccelHP accelerate in RPM/secondInputFLOATPR2_AccelLP accelerate in RPM/secondInputFLOATPR1_MaxHP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATSynCk_ByPassL25A_PERM - sync check bypassOutputBITOnLineOS1TstL97HP_TST1 - online HP overspeed testOutputBITOnLineOS1TstL97HP_TST2 - online HP overspeed testOutputBITOffLineOS2TstL97LP_TST2 - online HP overspeed testOutputBITOffLineOS1TstL97LP_TST2 - online HP overspeed test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ComposTrip1   | Composite trip 1                                  | Input  | BIT   |

| L5ESTOP1ESTOP 1 trip, TREG, J3InputBITL5ESTOP2ESTOP 2 trip, TREG, J4InputBITL5Cont1_TripContact 1 tripInputBIT::InputBITL5Cont7_TripContact 7 tripInputBITLPShaftLockLP shaft lockedInputBITBus FreqSF L 2 HzInputFLOATGenFreqSF 2 HzInputFLOATGenFreqDiffDV_ERR kV rms - generator low is negativeInputFLOATGenFreqDiffSDIFF2 slip Hz - generator slow is negativeInputFLOATGenPhaseDiffSDIFF2 phase degrees - generator lag is negativeInputFLOATPR1_AccelHP accelerate in RPM/secondInputFLOATPR3_AccelLP accelerate in RPM/secondInputFLOATPR1_MaxHP maximum speed since last zero speed in RPMInputFLOATPR2_MaxIP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATSynCk_BPassL25A_PERM - sync check permissiveOutputBITOnLineOS1TstL97HP_TST1 - online HP overspeed testOutputBITOnLineOS2TstL97HP_TST1 - online HP overspeed testOutputBITOffLineOS2TstL97HP_TST2 - offline IP overspeed testOutputBITOffLineOS3TstL97HP_TST2 - offline IP overspeed testOutput<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ComposTrip2   | Composite trip 2                                  | Input  | BIT   |

| L5ESTOP2ESTOP 2 trip, TREG, J4InputBITL5Cont1_TripContact 1 tripInputBIT::InputBITL5Cont7_TripContact 7 tripInputBITLPShaftLockLP shaft lockedInputBITBus FreqSFL 2 HzInputFLOATGenFreqSF 2 HzInputFLOATGenVoltsDiffDV_ERR kV rms - generator low is negativeInputFLOATGenPhaseDiffSSDIFF2 phase degrees - generator lag is negativeInputFLOATPR1_AccelHP accelerate in RPM/secondInputFLOATPR2_AccelIP accelerate in RPM/secondInputFLOATPR3_AccelLP accelerate in RPM/secondInputFLOATPR4_MaxHP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATSynCk_ByPassL25A_PERM - sync check permissiveOutputBITSynCk_ByPassL25A_DERM - sync check bypassOutputBITOnLineOS1TstL97HP_TST1 - online HP overspeed testOutputBITOnLineOS1TstL97LP_TST1 - online HP overspeed testOutputBITOffLineOS1TstL97LP_TST2 - online HP overspeed testOutputBITOffLineOS1TstL97LP_TST2 - online HP overspeed testOutputBITOffLineOS3TstL97LP_TST2 - online HP overspeed testOutputBIT <td>ComposTrip3</td> <td>Composite trip 3</td> <td>Input</td> <td>BIT</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ComposTrip3   | Composite trip 3                                  | Input  | BIT   |

| L5Cont1_TripContact 1 tripInputBIT::InputBITL5Cont7_TripContact 7 tripInputBITLPShaftLockLP shaft lockedInputBITBus FreqSFL 2 HzInputFLOATGenFreqSF 2 HzInputFLOATGen VoltsDiffDV_ERR kV rms - generator low is negativeInputFLOATGenPhaseDiffSFDIFF2 slip Hz - generator slow is negativeInputFLOATGenPhaseDiffSSDIFF2 phase degrees - generator lag is negativeInputFLOATPR1_AccelHP accelerate in RPM/secondInputFLOATPR3_AccelLP accelerate in RPM/secondInputFLOATPR3_AccelLP accelerate in RPM/secondInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATPR3_MaxLP maximum speed since last zero speed in RPMInputFLOATSynCk_PermL25A_PERM - sync check permissiveOutputBITSynCk_ByPassL25A_PERM - sync check bypassOutputBITOnLineOS1TstL97HP_TST1 - online HP overspeed testOutputBITOnLineOS1TstL97HP_TST2 - online HP overspeed testOutputBITOffLineOS2TstL97HP_TST2 - online HP overspeed testOutputBITOffLineOS1TstL97HP_TST2 - online HP overspeed testOutputBITOffLineOS1TstL97HP_TST2 - online HP overspeed testOutputBITOffLineOS2TstL97HP_TST2 - online HP overspeed test<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | L5ESTOP1      | ESTOP 1 trip, TREG, J3                            | Input  | BIT   |

| : : : Input BIT<br>L5Cont7_Trip Contact 7 trip Input BIT<br>LPShaftLock LP shaft locked Input BIT<br>Bus Freq SFL 2 Hz Input FLOAT<br>GenFreq SF 2 Hz Input FLOAT<br>GenVoltsDiff DV_ERR kV rms - generator low is negative Input FLOAT<br>GenFreqDiff SFDIFF2 slip Hz - generator slow is negative Input FLOAT<br>GenPhaseDiff SSDIFF2 phase degrees - generator lag is negative Input FLOAT<br>PR1_Accel HP accelerate in RPM/second Input FLOAT<br>PR2_Accel IP accelerate in RPM/second Input FLOAT<br>PR3_Accel LP accelerate in RPM/second Input FLOAT<br>PR1_Max HP maximum speed since last zero speed in RPM Input FLOAT<br>PR3_Max LP maximum speed since last zero speed in RPM Input FLOAT<br>SynCk_BYPass L25A_BYPASS - sync check permissive Output BIT<br>SynCk_ByPass L25A_BYPASS - sync check bypass Output BIT<br>OnLineOS1Tst L97HP_TST1 - online HP overspeed test Output BIT<br>OnLineOS1Tst L97HP_TST1 - online HP overspeed test Output BIT<br>OnLineOS1Tst L97HP_TST2 - online HP overspeed test Output BIT<br>OffLineOS1Tst L97HP_TST2 - online HP overspeed test Output BIT<br>OffLineOS3Tst L97HP_TST2 - online HP overspeed test Output | L5ESTOP2      | ESTOP 2 trip, TREG, J4                            | Input  | BIT   |